為什麼越累越難睡?當大腦想下班,「腸道」卻還在加班!

本文與 益福生醫 合作,泛科學企劃執行

昨晚,你又在床上翻來覆去、無法入眠了嗎?這或許是現代社會最普遍的深夜共鳴。儘管換了昂貴的乳膠枕、拉上百分之百遮光的窗簾,甚至在腦海中數了幾百隻羊,大腦的那個「睡眠開關」卻彷彿生鏽般卡住。這種渴望休息卻睡不著的過程,讓失眠成了一場耗損身心的極限馬拉松 。

皮質醇:你體內那位「永不熄滅」的深夜警報器

要理解失眠,我們得先認識身體的一套精密防衛系統:下視丘-垂體-腎上腺軸(HPA axis) 。這套系統原本是演化給我們的禮物,讓我們在面對劍齒虎或突如其來的危險時,能迅速進入「戰鬥或快逃」的備戰狀態。當這套系統啟動,腎上腺就會分泌皮質醇 (壓力荷爾蒙),這種荷爾蒙能調動能量、提高警覺性,讓我們在危機中保持清醒 。

然而,現代人的「劍齒虎」不再是野獸,而是無止盡的專案進度、電子郵件與職場競爭。對於長期處於高壓或高強度工作環境的人們來說,身體的警報系統可能處於一種「切換不掉」的狀態。

在理想的狀態下,人類的生理時鐘像是一場精確的接力賽。入夜後,身體會進入「修復模式」,此時壓力荷爾蒙「皮質醇」的濃度應該降至最低點,讓「睡眠荷爾蒙」褪黑激素(Melatonin)接棒主導。褪黑激素不僅負責傳遞「天黑了」的訊號,它還能抑制腦中負責維持清醒的食慾素(Orexin)神經元,幫助大腦順利關閉覺醒開關。

對於長期處於高壓或高強度工作環境的人們來說,身體的警報系統可能處於一種「切換不掉」的狀態 / 圖片來源:envato

對於長期處於高壓或高強度工作環境的人們來說,身體的警報系統可能處於一種「切換不掉」的狀態 / 圖片來源:envato

然而,當壓力介入時,這場接力賽就會變成跑不完的馬拉松賽。研究指出,長期的高壓環境會導致 HPA 軸過度活化,使得夜間皮質醇異常分泌。這不僅會抑制褪黑激素的分泌,更會讓食慾素在深夜裡持續活化,強迫大腦維持在「高覺醒狀態(Hyperarousal)」。 這種令人崩潰的狀態就是,明明你已經累到不行,但大腦卻像停不下來的發電機!

長期的睡眠不足會導致體內促發炎細胞激素上升,而發炎反應又會進一步活化 HPA 軸,分泌更多皮質醇來試圖消炎,高濃度的皮質醇會進一步干擾深層睡眠與快速動眼期(REM),導致睡眠品質變得低弱又破碎,最終形成「壓力-發炎-失眠」的惡行循環。也就是說,你不是在跟睡眠上的意志力作對,而是在跟失控的生理長期鬥爭。

從腸道重啟好眠開關:PS150 菌株如何調校你的生理時鐘

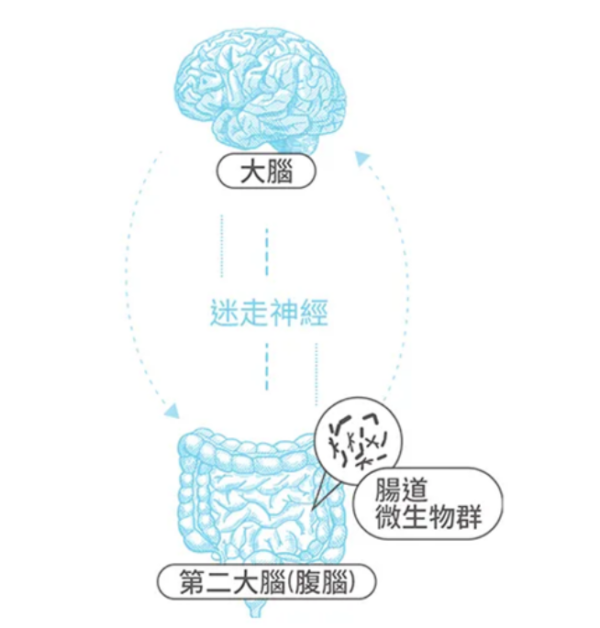

面對這種煞車失靈的失眠困局,科學家們將目光投向了人體內另一個繁榮的生態系:腸道。腸道與大腦之間存在著一條雙向通訊的高速公路,這就是「菌-腸-腦軸 (Microbiome-Gut-Brain Axis, MGBA)」,而某些特殊菌株不僅能幫助消化、排便,更能透過神經與內分泌途徑與大腦對話,直接參與調節我們的壓力調節與睡眠節律。這種菌株被科學家稱為「精神益生菌」(Psychobiotics)。

腸道與大腦之間存在著一條雙向通訊的高速公路,這就是「菌-腸-腦軸 (Microbiome-Gut-Brain Axis, MGBA)」/圖片來源:益福生醫

腸道與大腦之間存在著一條雙向通訊的高速公路,這就是「菌-腸-腦軸 (Microbiome-Gut-Brain Axis, MGBA)」/圖片來源:益福生醫

在眾多研究菌株中,發酵乳桿菌 Limosilactobacillus fermentum PS150 的表現格外引人注目。PS150菌株源於亞洲益生菌權威「蔡英傑教授」團隊的專業研發,累積多年功能性菌株研發經驗的科學成果。針對臨床常見的「初夜效應」(First Night Effect, FNE),也就是現代人因出差、換床或環境改變導致的入睡困難,俗稱認床。科學家在進行實驗時發現,補充 PS150 菌株能顯著恢復非快速動眼期(NREM)的睡眠長度,且入睡更快,起床後也更容易清醒。更重要的是,不同於常見的藥物助眠手段(如抗組織胺藥物 DIPH)容易造成快速動眼期(REM)剝奪或導致睡眠破碎化,PS150 菌株展現出一種更為「溫和且自然」的調節力,它能有效縮短入睡所需的時間,並恢復睡眠中代表深層修復的「Delta 波」能量。

科學家發現,即便將 PS150 菌株經過特殊的熱處理(Heat-treated),轉化為不具活性但保有關鍵成分的「後生元」(Postbiotics),其生物活性依然能與活菌媲美 。HT-PS150 技術解決了益生菌在儲存與攝取過程中容易失去活性的痛點,讓這些腸道通訊員能更穩定地發揮作用 。

在臨床實驗中,科學家觀察到一個耐人尋味的現象:當詢問受試者的主觀感受時,往往會遇到強大的「安慰劑效應」,無論是服用 HT-PS150 還是安慰劑的人,主觀上大多表示睡眠變好了。這種「體感上的進步」有時會掩蓋真相,讓人分不清是心理作用還是真實效益。

然而,客觀的生理數據(Biomarkers)卻揭開了關鍵的差異。在排除主觀偏誤後,實驗數據顯示 HT-PS150 組有更高比例的人(84.6%)出現了夜間褪黑激素分泌增加,且壓力荷爾蒙(皮質醇)顯著下降,這證明了菌株確實啟動了體內的睡眠調控系統,而不僅僅是心理安慰。

最值得關注的是,對於那些失眠指數較高(ISI ≧ 8)的族群,這種「生理修復」與「主觀體感」終於達成了一致。這群人在補充 HT-PS150 後,不僅生理標記改善,連原本嚴重困擾的主觀睡眠效率、持續時間,以及焦慮感也出現了顯著的進步。

了解更多PS150助眠益生菌:https://lihi3.me/KQ4zi

重新定義深層睡眠:構建全方位的深夜修復計畫

睡眠從來就不只是單純的休息,而是一場生理功能的全面重整。想要重獲高品質的睡眠,關鍵在於為自己建立一個全方位的修復生態系。

這套系統的基石,始於良好的生活習慣。從減少睡前數位螢幕的干擾、優化室內環境,到作息調整。當我們透過規律作息來穩定神經系統,並輔以現代科學對於 PS150 菌株的調節力發現,身體便能更順暢地啟動睡眠開關,回歸自然的運作節律。

與其將失眠視為意志力的抗爭,不如將其看作是生理機能與腸道微生態的深度溝通。透過生活作息的調整與科學實證的支持,每個人都能擁有掌控睡眠的主動權。現在就從優化生活型態開始,為自己按下那個久違的、如嬰兒般香甜的關機鍵吧。

與其將失眠視為意志力的抗爭,不如將其看作是生理機能與腸道微生態的深度溝通 / 圖片來源 : envato

與其將失眠視為意志力的抗爭,不如將其看作是生理機能與腸道微生態的深度溝通 / 圖片來源 : envato