文/麥軒誠、林執晰、曾介勇 | 台灣大學物理學系、電機工程學系學生

自從 19 世紀第一台電腦出現1開始,科學家們對電子科技的改良便從未停歇過,短短的 100 多年間,便從原本整間房間大小的電腦,變成現在能一手掌握的智慧型手機,這其中,電晶體和數位積體電路的出現功不可沒。

立大功的小小小小兵:積體電路

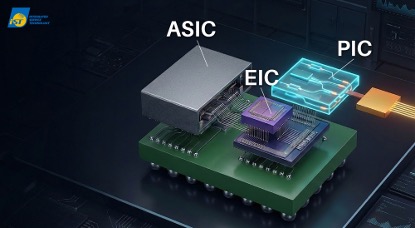

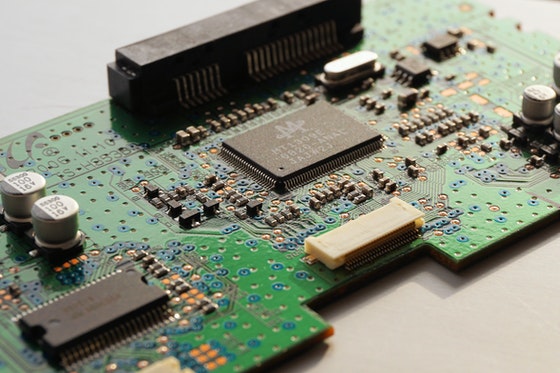

究竟為甚麼我們可以將萬千資訊、各種龐大功能濃縮成一隻小小的手機或是電腦呢?若是拆開各位的電腦或手機,一定可以看見有一塊黑黑方方的東西,這塊號稱電腦與手機的「大腦」,便是所謂的積體電路。

積體電路的構造就像細胞建構人體一樣,是由許多小小的電晶體所組成的,最大的好處即是能在小面積下裝入大量元件,具體到底有多大量呢?日前台積電公布的 3 奈米製程,每平方公釐就能裝載約 2.5 億個電晶體2,也就是說,光是一個指尖大小的積體電路,便能裝入十幾億個電晶體。

其中,「場效電晶體」(field-effect transistor, FET)是現今積體電路中最常使用的核心元件之一,隨著技術的進步,它的尺寸也不斷縮小,使相同面積的電子晶片上能有更多電晶體和其他元件,並讓資訊科技更快速的發展。

場效電晶體的功能是「控制電流的開關與大小」,當我們透過訊號施加不同電壓在閘極(gate electrode,中上)時,就可以改變汲極(drain,右)與源極(source,左)之間通道(channel)的狀態,並進而改變電流。

那麼一般科學家是如何讓電晶體越來越小呢?讓電晶體更迷你的重點就在於:讓汲極與源極之間的電流通道(channel)變小。

開關失靈、耗電與漏電的技術挑戰

但隨著電晶體的尺寸越來越小,科學家在技術的研發上遇到了三大難題。

首先,傳統電晶體的通道是以矽作為原料,而「閘極」作為電晶體的「工作開關」,當它的尺寸越來越小時,控制通道電位的能力也會下降,也就是說,電晶體作為開關的能力會喪失,就好比一個關不起來的水龍頭。

第二個困境,雖然尺寸變小,但科學家已經難以降低積體電路中所需要的工作電壓了,當工作電壓無法降低時,就會帶來比較高的功率消耗,產生不必要的耗電註1。

第三個問題,即使傳統場效電晶體已經關閉,當尺寸變小時,會更難完全阻擋電子在通道之間流動,並產生漏電流。在通道變小的情況下,僅是源極與汲極之間的電場便能使電流通過,產生漏電流的問題。

尤其當電子產品的尺寸、臨界電壓都越來越小的情況下,漏電流將造成更嚴重、更明顯的影響!在電晶體未切換開、關狀態時的穩定狀態時,這些漏電流會順著周遭的電壓差亂跑,造成額外的能量消耗,產生不必要的耗電。

同時,這些能量消耗所產出的廢熱也會進一步的影響路徑附近電晶體的工作表現,影響其他電晶體的性能,並出現「過熱」的現象。

新興材料與穿隧式電晶體幫助突破瓶頸!

為了解決這三大難題,近期科學家3研發出了新一代的電晶體——ATLAS – TFET (atomically thin and layered semiconducting-channel tunnel-FET) 。

ATLAS – TFET 是來自新興材料「平面材料過渡金屬硫屬化合物」(Transition metal dichalcogenide, TMD) 與「穿隧式場效電晶體」(tunnel field-effect transistor, TFET) 的結合,改善了過往電晶體因為小尺寸而帶來的各種缺點。

首先,相比傳統電晶體常用的矽、鍺或三、五族元素作為通道,ATLAS – TFET 的通道原料是平面材料過渡金屬硫屬化合物,而平面材料過渡金屬硫屬化合物可以做到非常、非常的薄,藉此縮減電晶體通道的大小,滿足電晶體尺寸縮減的需求。最棒的是,已經有許多實驗證實,當科學家使用這種材料製作電晶體的電流通道時,就算通道變小、變短,閘極對於通道的控制能力也不會因此而下降!

透過這種材料製作電流通道,科學家終於解決了第一個問題。

此外,研究也顯示,比起傳統場效電晶體,ATLAS – TFET 的次臨界擺幅(subthreshold swing)註2縮減了許多,而隨著次臨界擺幅下降,ATLAS – TFET 的工作電壓也會變小。

從數據上來看,現代常用的電晶體工作電壓為 0.7 伏特,而 ATLAS – TFET 的工作電壓可以縮小到 0.1 伏特,由此可知,ATLAS – TFET 也完美的改善了第二個問題,讓電晶體的工作電壓變得更低,減少了不必要的功率消耗,避免多餘的耗電。

除了電流通道的材料與眾不同,ATLAS – TFET 採用了「穿隧式場效電晶體」,在這種電晶體的結構中,來自源極的電子會藉由「量子穿隧效應」直接穿隧至通道,並產生電流,也就是說,電流傳導的方式跟傳統場效電晶體完全不同,

綜觀以上三點,ATLAS – TFET 可以說取得充分的突破!雖說目前來看,該電晶體目前仍在實驗「電晶體本身」的性質,還很難馬上被應用在數位積體電路,大家可以想像雖然他的單一「細胞」表現很好,但是還不能很好的跟其他細胞或是組織結合在一起。

雖然 ATLAS – TFET 距離實際應用還有一段距離,但它確實提供了充滿吸引力的研究方向,以期實現理想的工程目標,科學家也表示, ATLAS – TFET 若能跟現行的其他技術整合,我們可以期待未來相關電子元件的功能可以越來越強大!

註解

- 積體電路所消耗功率,與積體電路中電晶體狀態切換的頻率與電晶體的工作電壓成正比。頻率更快相當於同一段時間內能做更多次操作,這樣才能在更短的時間完成更多事。而以相同頻率的基準比較,更高的工作電壓代表更高的功率消耗,因此抑制工作電壓大小可以非常有效的抑制功率消耗,也就是說,第二個問題導致了多餘功率消耗的問題難以解決,最直接的影響就是會並產生有不必要的耗電。

- 工作電壓被臨界電壓(threshold voltage)、次臨界擺幅(subthreshold swing)所決定,因為傳統場效電晶體的臨界電壓與次臨界擺幅受到了限制,導致工作電壓幾乎無法再更低。其中,次臨界擺幅(subthreshold swing)的定義為當汲極電流增加十倍時,所需要增加的閘極電壓,是衡量電晶體開、關狀態相互轉換的速率的一項重要性能指標。

致謝

本文源自於臺灣大學物理學系電子學的課程報告,感謝朱士維教授與程暐瀅助教的協助。

參考資料

- When was the first computer invented? – Computer Hope

- TSMC Plans to Start Production of 3nm Plus Process in 2023

- Deblina Sarkar, Xuejun Xie, Wei Liu, Wei Cao, Jiahao Kang, Yongji Gong, Stephan Kraemer, Pulickel M. Ajayan & Kaustav Banerjee. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95(2015).