矽光子是近年熱門議題,晶圓大廠計劃將先進封裝整合 CPO 及矽光子技術,預計兩年後完成並投入應用。早在 2020 年,Intel 就指出矽光子將是先進封裝發展的關鍵,如今矽光子已真正成為半導體產業的核心研發方向。面對這次「電」轉「光」的新革命,您準備好了嗎?

本文轉載自宜特小學堂〈光革新突破半導體極限 矽光子晶片即將上陣〉,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

隨著半導體積體電路技術的不斷發展,我們見證了摩爾定律的演進,元件尺寸的微縮和新材料的應用,都是為了提高單位面積內的元件數量,以加速 IC 的運算速度,同時改善散熱效能和節省能源。然而,隨著尺寸的微縮接近物理極限,製程技術面臨挑戰,良率問題也隨之浮現。

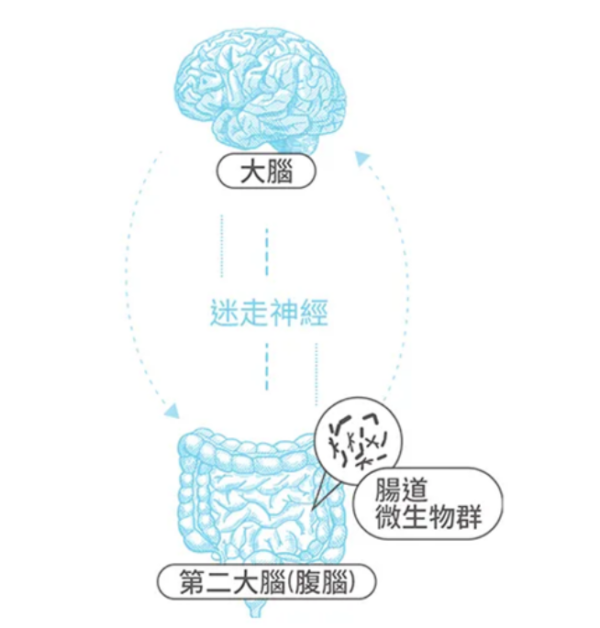

因應這一挑戰,專家開始探索將不同功能的 IC 集合成單一晶片、採用 3D 堆疊封裝技術等新途徑,但這些技術的核心仍然是用金屬線連接各個元件。自從晶片問世以來,「電子」一直是主要的訊號傳輸媒介,它的傳輸速度直接決定了晶片的性能。近年來高效能運算(HPC)、人工智慧(AI)、雲端數據等需求爆炸性成長,如何能突破限制實現更高效能的傳輸呢?於是大家把目光轉向了「光子」,藉由更快速的「光子」引入,是否可以加快元件的運作呢?

什麼是矽光子(Silicon photonics,簡稱 SiPh)?

矽光子(Silicon photonics,簡稱 SiPh) 是一種結合電子與光子的技術,是將光路微縮成一小片晶片,利用光波導在晶片內傳輸光信號。若能將處理光訊號的光波導元件整合到矽晶片上,同時處理電訊號和光訊號,便可達到縮小元件尺寸、減少耗能、降低成本的目標,但目前矽光子仍有許多技術難題需克服。

光通訊運用的「光纖」系統,能於世界各地以每秒數萬億 bit 的速度傳送數據,1968 年貝爾實驗室工程師很早就想到了。到了 21 世紀初發現光子技術不僅能在國與國之間做數據的傳遞,亦可在數據中心甚至是 CPU 之間,乃至於在晶片與晶片之間做數據傳輸。之所以採用「光」是因為玻璃(SiO2)對於光來說是透明的,不會發生干擾的現象,基本上,可以透過在 SiO2 中,結合能夠傳遞電磁波的光波導(Waveguide)通路來高速地傳輸數據。

而矽(Si)材料的折射率(Refractive index)對比在紅外線的波長下高達 3.5,這也意味著,它比許多其他光學中所用的材料,更能有效地控制光的彎折或減速。一般光學傳輸的波長是 1.3 和 1.55 微米,在這兩個波段下矽材料不會吸收光線,因此光線能夠直接穿透矽材料。這種相容性使矽基設備能夠長距離傳輸大量數據,不會明顯失去訊號。

因此,矽光子技術透過原本 CMOS 矽(Si)的成熟技術,結合光子元件製程,可以使處理器核心之間的資料傳輸速度提高數百倍以上,且耗能更低;CPO(共同封裝光學)則是利用矽光子技術,將光通訊元件和交換器做整合,放在同一個模組內,這樣能縮短傳輸路徑,並在高速傳輸時,降低延遲與功耗。現今各大廠的目標是透過CPO和矽光子,實現更高效的光電封裝整合,大幅提升傳輸性能。

除了前面提到高效運算跟人工智慧需求不斷增加,光學雷達、生醫感測也非常適合使用光子元件,世界前幾大 IC 製造商都相繼發表矽光子是未來 IC 技術的關鍵及趨勢,本文將與大家分享相關文獻,了解矽光子元件組成與決定效能的關鍵。

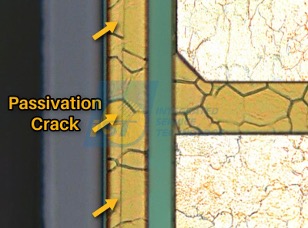

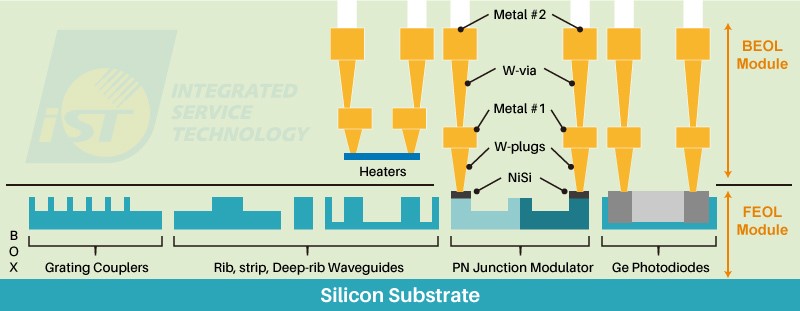

矽光子元件組成,材料以「鍺」為首選

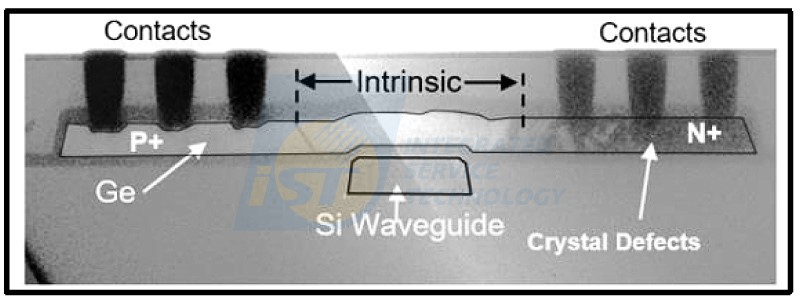

矽光子元件的基本組成是使用能將「光」轉換成「電」訊號的 p-i-n diode(PIN二極體)光電偵測器,加上傳輸訊號的光波導(Wave guide)與電訊號轉成光子的調變器(Modulator)、耦合器(Coupler)等所組合成的一個單晶片,斷面的結構大致如圖一所示。

其中最關鍵的製造技術即在圖一最右側 PIN 二極體,首選的半導體材料為鍺(Ge),因為鍺具有準直接能隙(Quasi-Direct band gap)且僅有 0.8eV 小於光子能量,能夠有效吸收光並轉換成電訊號,並且對於光的吸收係數很高,更適合用於光電偵測器,是一種非常好的取代材料。

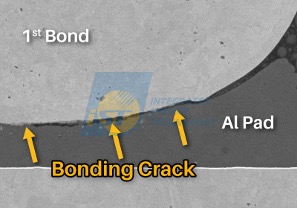

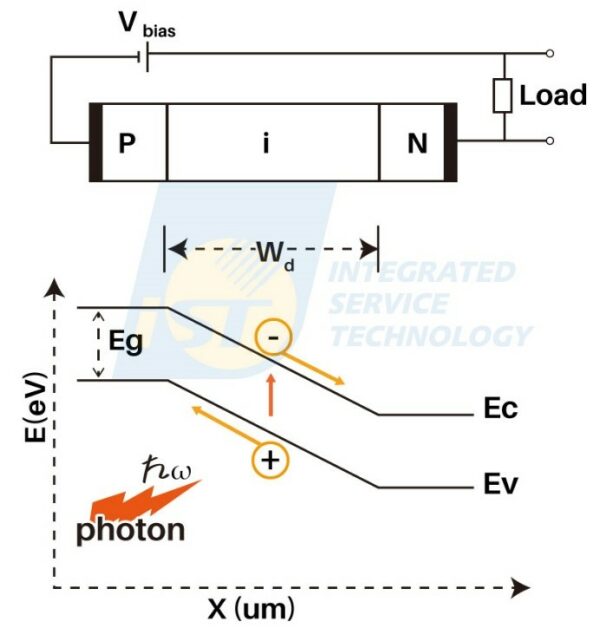

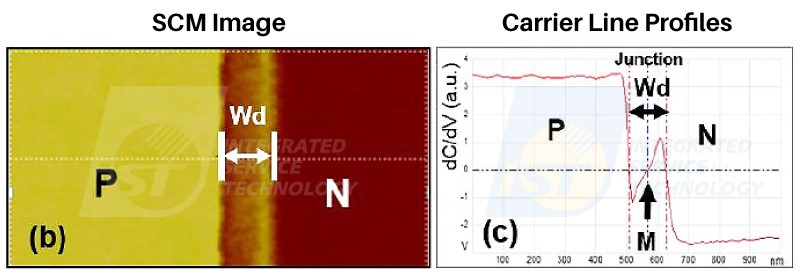

PIN 是由一組高摻雜P (p+)型區和N (n+)型區之間夾著一層本質(Intrinsic)區所組成。在負偏壓下二極體的空乏寬度(Depletion width, Wd)會擴展至整個本質層。如圖二下能帶結構所示,當入射到本質層中的光子被吸收後,於導電和價電帶間產生電子–電洞對的漂移而形成電流。在矽光子元件的研發中最重要的方向,就是在不影響常規 CMOS 元件的特性下透過調整光電偵測器 PIN 的製程,且能使效能與頻寬達到最佳化。

如何辨別 Ge-PIN 的品質?

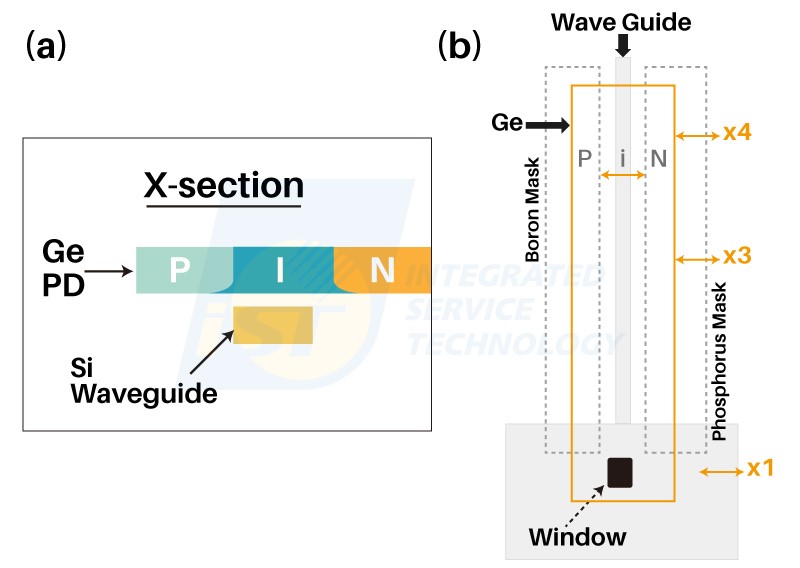

先以圖三簡單的說明一顆單晶片的設計,Ge-PIN 光電偵測器與 Si -光波導的相對位置,(a)圖為剖面結構示意圖,光波導位於本質層下方,(b)圖為正面 Layout。

因為 Ge-PIN 的品質差異會影響到偵測器的光電效能,鍺(Ge)的磊晶製程與 矽(Si)之間會有晶格不匹配與離子植入產生的差排缺陷等影響品質,圖四是Ge-PIN藉由穿透式電子顯微鏡(TEM)的觀察,可以明顯看出在本質層(Intrinsic)與 P 區均呈現亮區,代表沒有明顯缺陷,反觀在右側的 N 區則呈現暗灰色,這應該是源自於離子植入製程所產生的晶格缺陷。(延伸閱讀:破解半導體差排軌跡 TEM 技術找出晶片漏電真因)

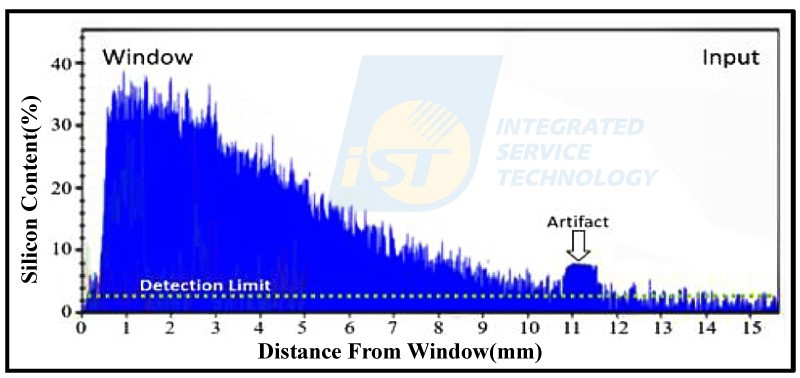

此外,藉由 EDS 來分析波導中的矽(Si)是否有朝向 Ge-PIN 擴散的情形。圖五為鍺(Ge)層中沿著波導方向矽(Si)的含量分佈。矽(Si)摩爾百分比從接觸窗(Window)最高約 35%,向輸入側減少至低於 EDS 檢測極限的 2%,約是在 11mm 的位置處,表示發生明顯的擴散現象。

如何觀察影響光電偵測器效能空乏區寬度的大小?

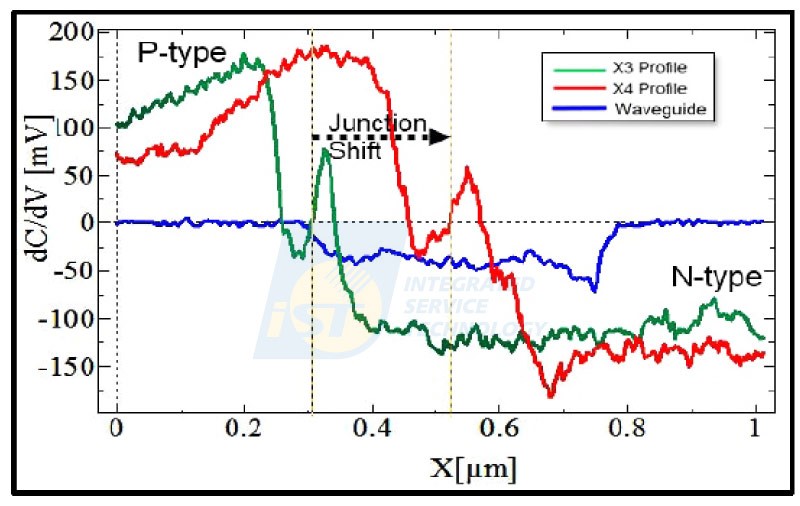

矽光子元件主要是採用與矽基產品相同的 CMOS製程,藉由掃描電容顯微鏡(SCM)的分析技術可以量測 PIN 在不同製程條件下,觀察本質層中空乏區寬度(Wd)的變化,圖六說明經由 SCM 二維載子分布圖(Mapping)影像以及從一維載子線分佈(Line Profile),分別能區分 P/N 接面(Junction)的位置與 Wd 的示意圖。

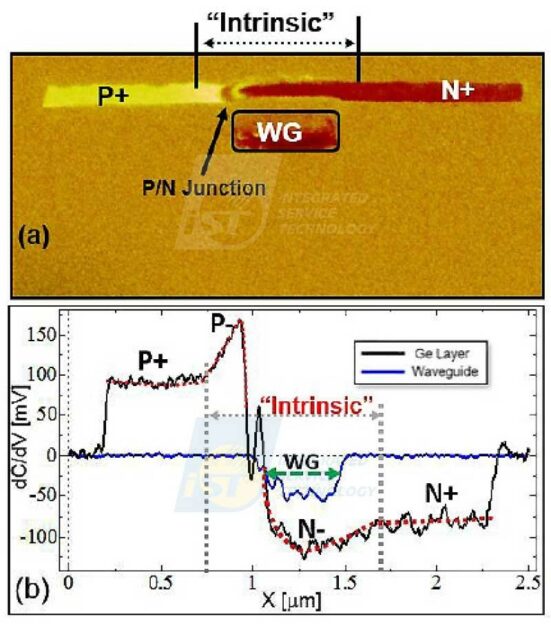

圖七:在圖三(B)中 x3 位置的斷面 SCM (a)2D mapping 影像與(b)1D Line profile。 [7]

在圖三中 X3 與 X4 兩位置區域的剖面 SCM 一維載子分布的結果於圖八中,可以量得 p/n 接面位置偏移了約 215nm (兩條虛線間距)。上述都是透過 SCM,可觀測出空乏區寬度(Wd)的變化,而空乏區的寬度決定電流流過的多寡,將會直接影響到元件品質與性能。

本文中談到離子植入產生的晶格缺陷或是矽波導朝向本質層擴散現象,以及 N/P dopant 擴散速率的差異影響 Wd 寬度等,這些要素皆決定了矽光子元件的品質,都是目前研發單晶片矽光子製程技術,所需面對的課題。

此外,在設計 Waveguide 材料或形狀,以及其他相關製程的研發中,均可藉由奈米材料分析技術如 TEM、EDS 與 SCM 等,宜特科技擁有大量材料分析實戰經驗,可以提供客戶有效的濃度分布的數據分析,並以此依據改善研發製程細節。

事實上,現有相關矽光子產品大多是將數位交換晶片與光收發模組(Transceiver)利用先進封裝包裝在一起,就是使用我們前面所說的 CPO(Co-Packaged Optics)的方式來商品化,但這種產品仍有能耗與體積的問題,未來採用「矽光子單晶片」才能真正達到短小節能的目標,矽光子技術可以提供高速、節能的整合解決方案,從而徹底改變資料中心、人工智慧、電信、感測和成像以及生物醫學應用等行業。

宜特科技長期觀察半導體產業趨勢,我們認為儘管矽光子技術存在整合和設備製造相關的挑戰,相信各家大廠仍會持續加速研發腳步,在全球共同努力下,突破摩爾定律關鍵技術的誕生終將指日可待。

本文出自 宜特科技。

參考文獻:

- [1] Daniel Benedikovic*, Léopold Virot, Guy Aubin, Jean-Michel Hartmann, Farah Amar, Xavier Le Roux, Carlos Alonso-Ramos, Éric Cassan, Delphine Marris-Morini, Jean-Marc Fédéli, Frédéric Boeuf, Bertrand Szelag and Laurent Vivien, “Silicon–germanium receivers for short-wave-infrared optoelectronics and communications”, Nano-photonics 2021; 10(3): 1059–1079

- [2] -[8] J. Nxumalo, Y. Wang, M. Iwatake, C. Molella, A. Katnani, J. Orcutt, J. Ayala, K. Nummy, “Characterizing junction profiles in Ge photodetectors using scanning capacitance microscopy (SCM) and electron holography”, 978-1-5386-4513-0/18 ©2018 IEEE