本文轉載自中央研究院研之有物,泛科學為宣傳推廣執行單位。

- 整理撰文/郭雅欣、簡克志

- 美術設計/蔡宛潔

手機越來越快, IC 晶片卻越來越小,關鍵是「光學微影」

自光學微影技術出現以來,積體電路(Integrated circuit, IC)的體積跟隨著摩爾定律不斷縮小,到我們踏入 5 奈米量產世代的今日,IC 可以說足足縮小了百萬倍!這樣的成果並非一蹴可幾,而是多年來半導體研發人員和工程師的心血累積而成。中央研究院 111 年知識饗宴的科普講座中,林本堅院士以「光學微影縮 IC 百萬倍」為題目,分享了光學微影這一路走來,如何將半導體元件尺寸愈縮愈小、推向極限。

隨著積體電路(IC)與半導體製程的進展,我們的手機、平板等 3C 產品,體積愈來愈小,速度卻愈來愈快,功能也愈來愈多、愈強大。這歸根究柢,是因為現在的半導體技術把 IC 愈做愈小了,在 3C 產品中可以放入的元件數量愈來愈多,自然能做的事情更多了,效率也增加了。

IC 愈做愈小的關鍵技術在於光學微影(Optical Lithography)。光學微影簡單來說,就是在製作元件的過程中,將元件的組成材料依所需位置「印」在半導體晶圓上的技術。能印出愈精細的圖案,就能製作出愈小的元件。

如果讀者好奇手機或電腦的 IC 晶片是怎麼做出來的?請參考以下蔡司公司製作的影片,解釋了晶片從原料到封裝的整個過程,影片中的曝光(exposure)步驟,就是我們這篇文章要介紹的主題。

衡量元件尺寸的關鍵指標之一為「電晶體閘極長度」(Gate length),這個數字與 IC 速度直接相關。以場效電晶體來說,閘極長度愈小,電流可以花更少時間通過電晶體的汲極和源極。

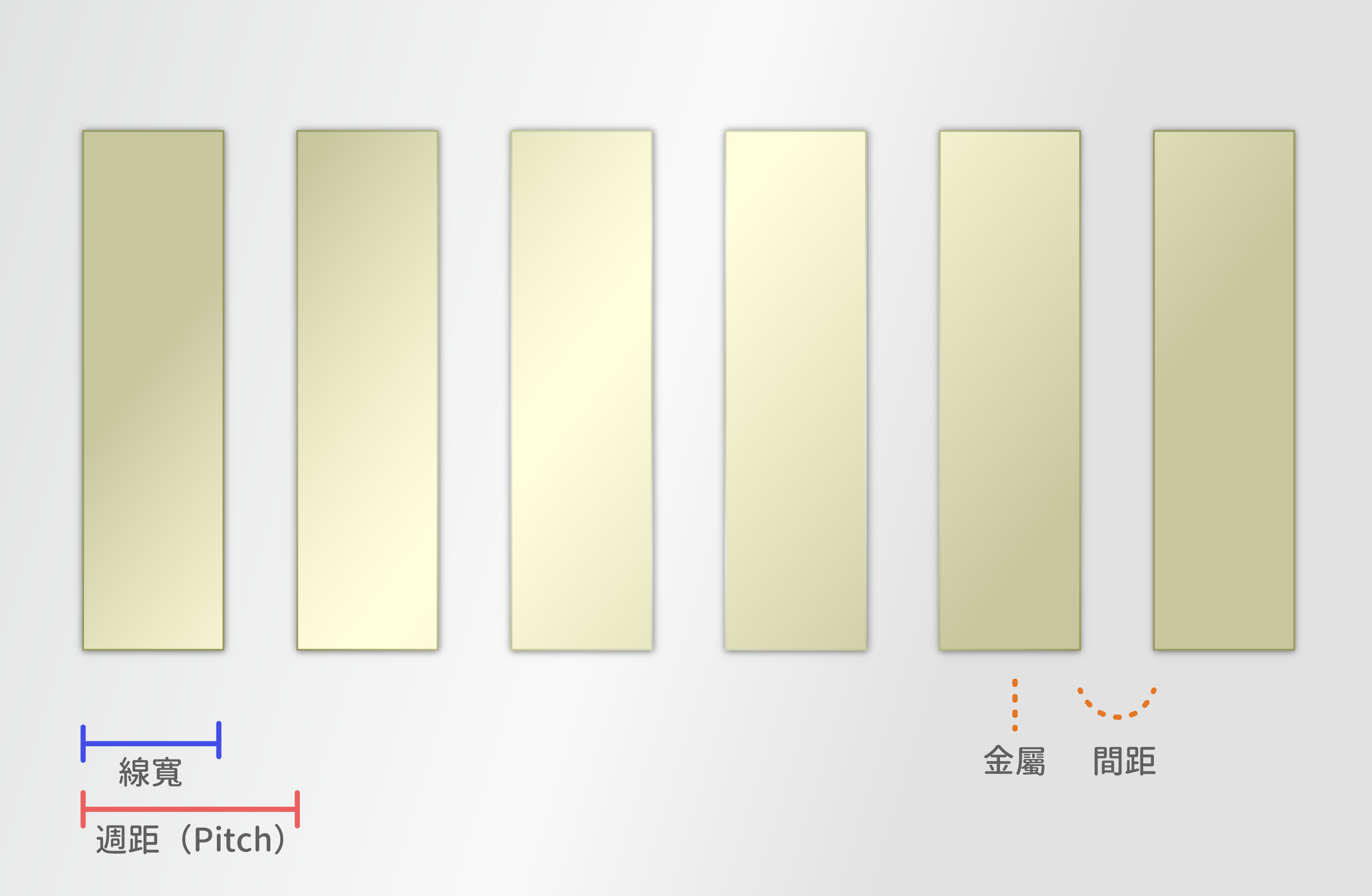

如果要表示元件微縮的程度,另一個關鍵指標為線寬和週距(Pitch),通常以金屬層線與線的週距為參考基準,週距做得愈小,線寬也愈小,元件微縮程度愈高,見以下示意圖。

如今,到了單位數奈米的世代(例如 7 奈米或 5 奈米製程),這些數字已經逐漸演變為僅是世代的號誌。雖然 IC 還是愈小愈好,但是新世代製程工藝可能代表運算快、密度高、價錢便宜等其他綜合優點。

那 IC 目前到底縮小了多少呢?我們可以先有個概念,如果把每個世代視為實際尺寸來看,自從 1980 年代有光學微影技術以來,線寬從一開始的 5,000 奈米,如今已降到 5 奈米、甚至往 3 奈米邁進了。線寬不斷往下縮小,每一代大約縮小為上一代的 0.7 倍,到 5 奈米已經是第 21 代。經過了這樣的「代代相傳」,線寬縮小了 1,000 倍,換算下來,同一面積所能放入的元件數量高達原本的 100 萬倍!

光學微影技術如魔法般把線寬一步步縮小,靠的是多年來研發人員一步步的努力。林本堅院士在「光學微影縮 IC 百萬倍」這場科普講座中,一一細數其中的關鍵改良,以及箇中挑戰。

IC 晶片縮小術,秘訣在於追求最小線寬

讓我們先從一個核心的光學解析度公式開始:

半週距(Half Pitch)= k1λ/sinθ

半週距:一條線寬加上線與線的間距後乘以 1/2。曝光解析度高時,半週距可以做得愈小,意味著線寬可以愈小。

k1:一個係數,與製程有關,縮小半週距的關鍵,是所有半導體工程師致力縮小的目標。

λ:微影製程中使用的光源波長,從一開始的 436 奈米,現已降到 13.5 奈米。

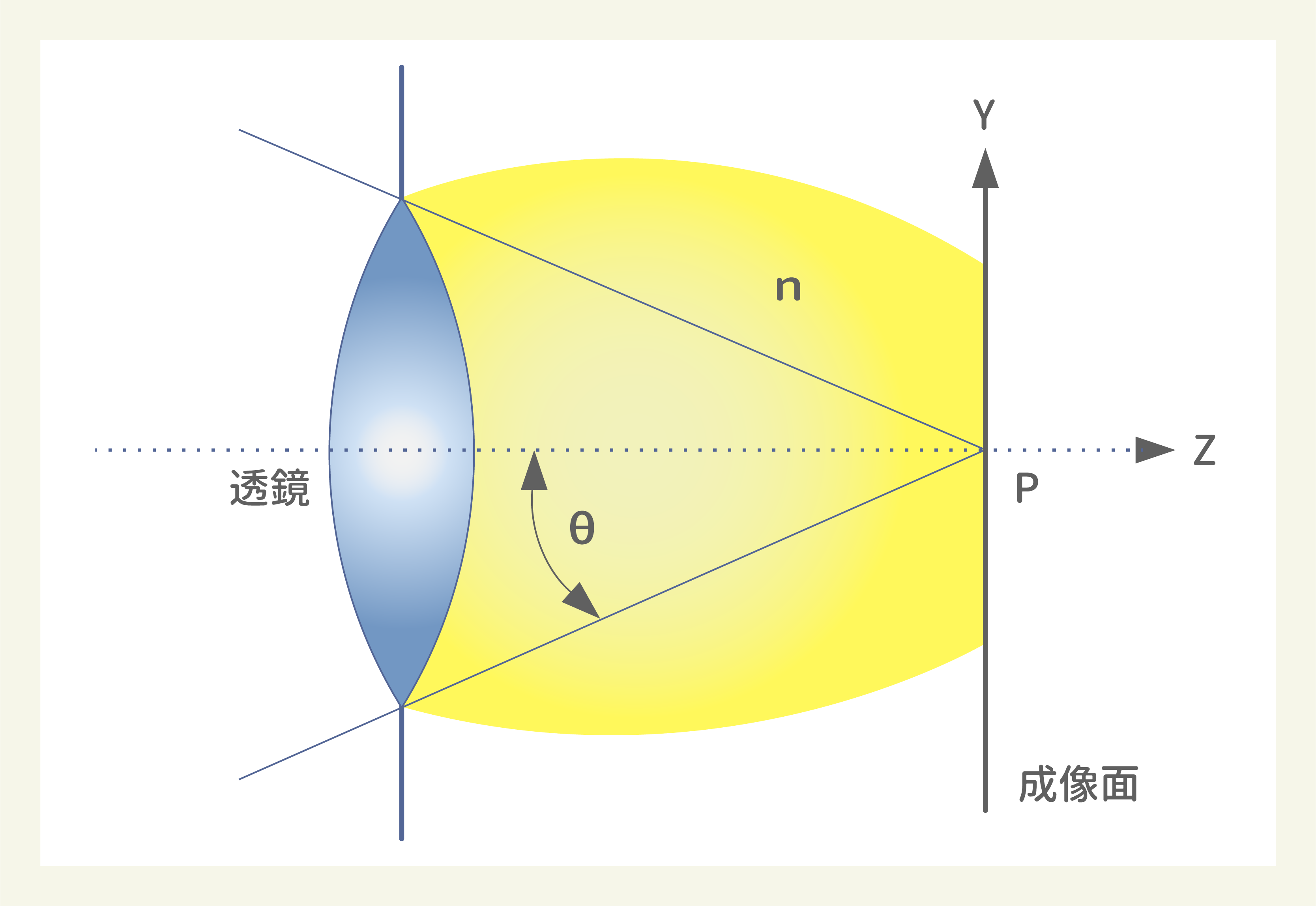

sinθ:與鏡頭聚光至成像面的角度有關,基本上由鏡頭決定。

由於光在不同介質中,波長會有所改變,因此我們在考慮如何增加解析度時,可將鏡頭與成像面(晶圓)之間的介質(折射率 n)一併納入考量,將 λ 改以 λ0/n 表示,λ0 是真空中的波長。

半週距(Half Pitch)= k1λ0/n sinθ

因此,增加曝光解析度(半週距 ↓)的努力方向為:增加 sinθ、降低 λ0、降低 k1、增加 n。

另一方面,為了讓微影製程有足夠大的曝光清晰範圍,鏡頭成像的景深(DOF)數字愈大愈好(註1),但是景深變大的副作用是——半週距也會跟著變大,因此在製程改良上必須考慮兩者的平衡或相互犧牲。

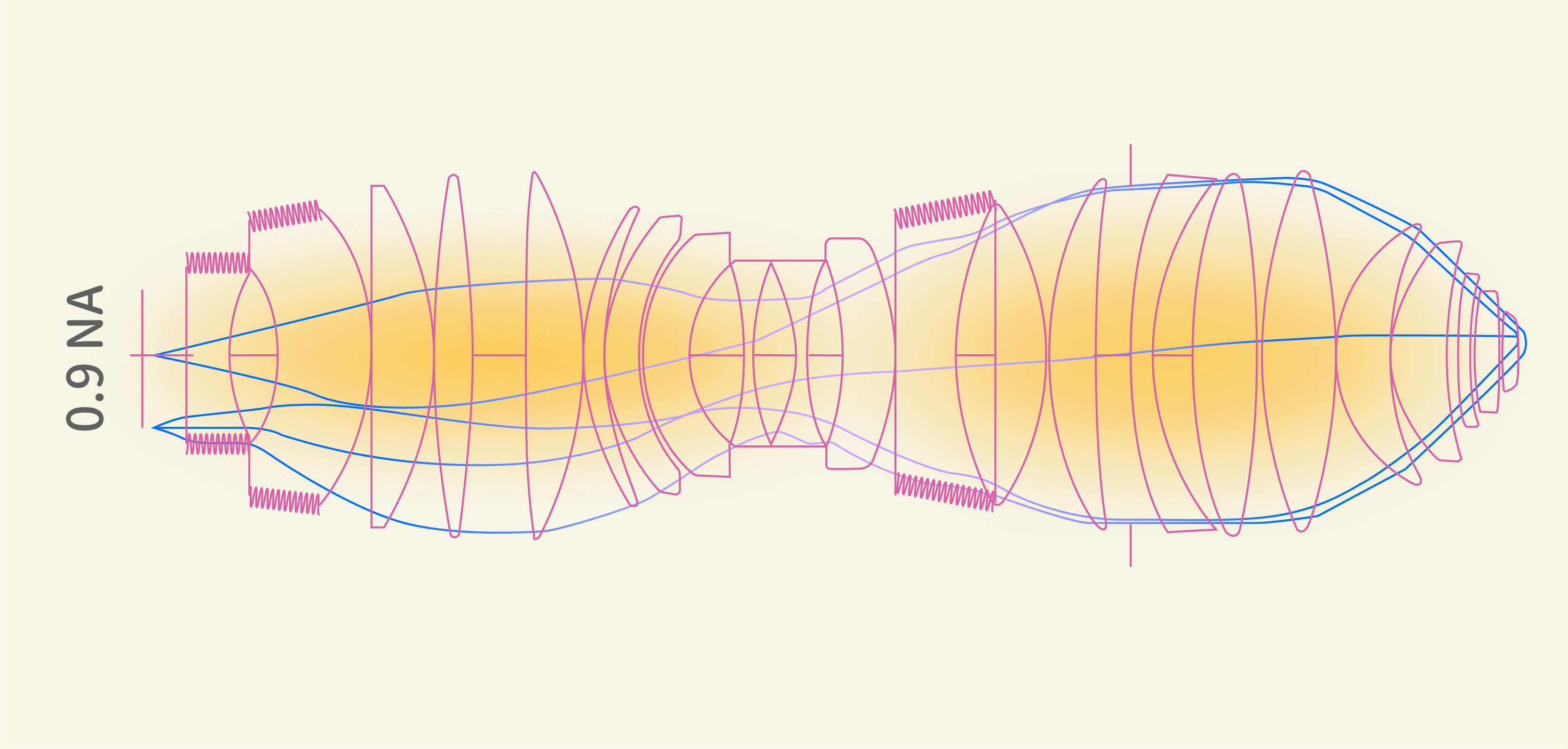

巨大複雜的鏡頭,都是為了增大 sinθ

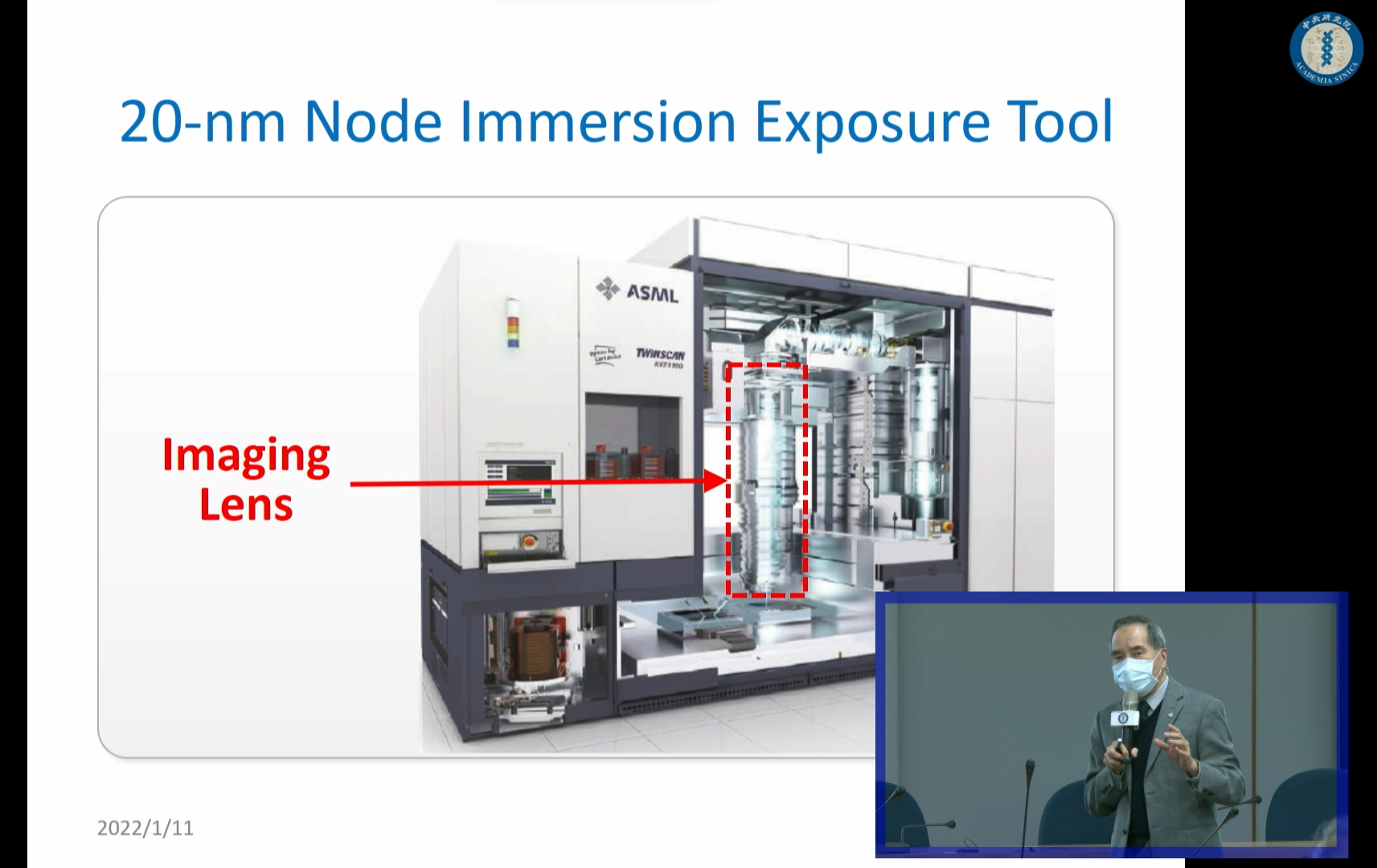

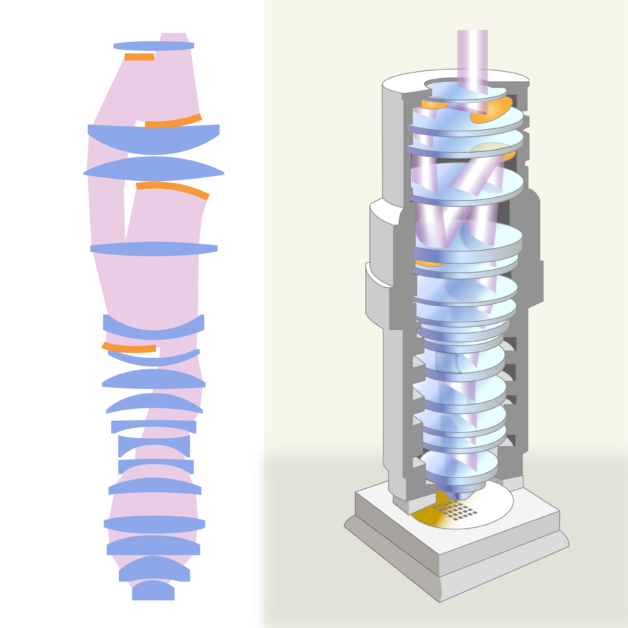

sinθ 與鏡頭聚光角度有關,數值由鏡頭決定,sinθ 愈大,解析度愈高。光學微影所使用的鏡頭,並不如我們平常使用的相機或望遠鏡那般簡單——而是由非常多大大小小、不同厚薄及曲率的透鏡,經過精確計算後,仔細堆疊組成的(如下圖)。

這樣極其精密的鏡頭,林本堅透露:「6,000 萬美金的鏡頭已經不值得驚奇了,一億美金都有可能。」鏡頭做得這樣複雜、巨大又昂貴,是為了盡可能將 sinθ 逼近它的極值,也就是 1,他接著說:「目前的鏡頭可將 sinθ 值做到 0.93,這已經是非常辛苦了。」

鏡頭材料精準的搭配:縮短波長

第二個方法是縮短波長。雖說改變使用的光源,就能得到不同的波長,但因為不同波長的光經過透鏡後的折射方向不同,因此鏡頭的材料也必須相應改變。林本堅表示,當波長愈縮愈短,「我們能選擇的鏡頭材料也愈來愈少,最後就只有那兩三種可以用。」

用少數幾種材枓來調適光源的頻寬愈來愈難。所以後來大家轉而選擇單一種合適的材料,並針對適合這種材料的波長,將頻寬盡量縮窄。林本堅說:「連雷射的頻寬都不夠窄小,現在把頻寬縮窄到難以想像的程度。」

另一種解決問題的方法,則是在鏡頭的組成中加入反射鏡,這樣的鏡頭組合稱為反射折射式光學系統(Catadioptric system)。因為不管是什麼波長的光,遇到鏡面的入射角和反射角都是相等的,因此若能以一些反射鏡面取代透鏡,就可以增加對光波頻寬的容忍度。

後來到了 13.5 奈米(極紫外光,EUV)的波長時,甚至必須整組鏡頭都使用反光鏡,稱為全反射式光學系統(All reflective system),可參考以下 ASML 公司的展示影片。林本堅表示,這種全反射鏡的系統,必須設計得讓光束相互避開,使鏡片不擋住光線。此外,相較於透鏡穿透的角度,鏡面反射的角度對誤差的容忍度更低,鏡面角度必須非常非常精準。以上這些都增加了設計的困難度。

曝光波長的改變還會牽涉到底下的曝光光阻,光阻材料從化學性質、透光度到感光度等各項特性,都必須隨著曝光波長的改變而調整,「這是個浩大的工程。其中感光速度非常重要,是節省製造成本的關鍵」,林本堅說。

值得一提的是,光阻材料的感光速度在微縮 IC 的歷史中相當重要。1980 年代,時任 IBM 的 C.G. Willson 和 H. Iro 率先提出一種以化學方式放大光阻感光速度的方法,將感光速度提升了 10~100 倍,大幅增加了曝光效率。這項重大發明,讓 C.G. Willson 在 2013 年榮獲「日本國際獎」(Japan Prize),可惜當時 H. Iro 博士已故,無法一同受獎。

提高解析度的關鍵:降低 k1

提高解析度的重頭戲就在於如何降低 k1。林本堅說:「你可以不用買昂貴的鏡頭,也可以不選用需要很多研發功夫的新波長。只要你能用聰明才智與創造力,將 k1 降下來。」

首先是「防震動」,就好像拍照開防手震功能一樣,在晶圓曝光時設法減少晶圓和光罩相對的震動,使曝光圖形更加精準,恢復因震動損失的解析度。再來是「減少無用反射」,在曝光時有很多表面會產生不需要的反射,要設法消除。林本堅表示,改良上述這兩項, k1 就可以達到 0.65 的水準。

提高解析度還可以使用雙光束成像(2-beam Imaging)的方法,分別有「偏軸式曝光」(Off-Axis Illumination, OAI)及「移相光罩」(Phase Shift Mask, PSM)兩種。

偏軸式曝光是調整光源入射角度,讓光線斜射進入光罩,原本應通過光罩繞射的三束光(1 階、0 階與 -1 階),會去掉外側的一束光(1 階或 -1 階),只留下其中兩束光(例如 0 階和 1 階)。透過角度的調整,可以很巧妙地讓這兩道光相互干涉來成像,使解析度增加並增加景深。

移相光罩則是在光罩上動些手腳,讓穿過相鄰透光區的光,有 180 度的相位差。相位差 180 度的光波強度不會改變,只是振幅方向相反。如此一來,相鄰透光區的光兩兩干涉之後,剛好會在遮蔽區相消(該暗的地方更暗),增加透光區與遮蔽區的對比,進而提高解析度。

「這兩種做法都可以讓 k1 減少一半。」林本堅笑說:「可惜這兩種方法都是用 2-beam Imaging 的概念,不能疊加起來使用。」

目前業界多半多半使用偏軸式曝光,林本堅表示:「移相光罩一方面比較貴,另一方面,它不能任意設計圖案,必須考量鄰近相位不抵消的問題。」利用各種降低 k1 的技術,目前已將 k1 降到 0.28,「這幾乎是這些技術所能做到的 k1 極限了。」

要進一步降低 k1 ,還有辦法!就是用兩個以上的光罩,稱為「多圖案微影」。簡單來說,它將密集的圖案分工給兩個以上圖案較寬鬆的光罩,輪流曝光在晶圓上,這樣可以避免透光區過於接近,使圖案模糊的問題。缺點則是因為曝光次數加倍,等於效率降低了一半。

鏡頭與晶圓之間的介質:浸潤式微影技術

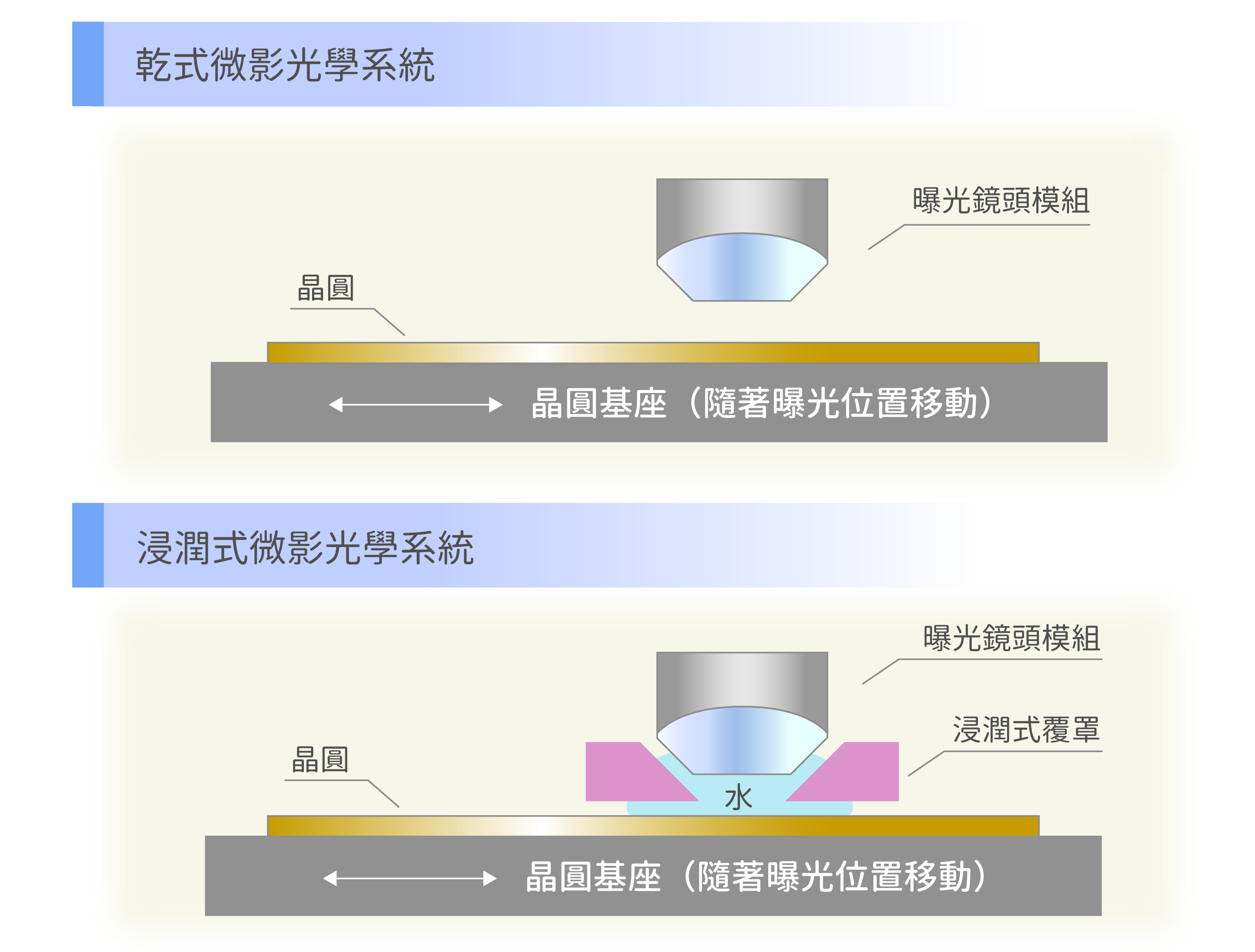

在增加微影解析度的路上,最後一個可以動手腳的就是鏡頭與晶圓之間的介質。由林本堅提出的浸潤式微影技術中,將鏡頭與晶圓之間的介質從折射率 n~1 的空氣,改成n= 1.44 的水(對應波長為 193 奈米的光),形同將波長等效縮小為 134 奈米。

浸潤式微影技術讓半導體工藝在 12 年內往前走了 6 代——從 45 奈米直到 7 奈米。林本堅補充說,這個技術的優勢在於「你可以繼續使用同樣的波長和光罩,只要把水放到鏡頭底部和晶圓之間就好。」

不過,林本堅話鋒一轉。「我說得很輕鬆,把水放進去就好。但這背後其實有很多技術。」例如水中的空氣可能讓水產生氣泡,必須完全移除。另外,放進去的水必須很均勻,在透光區照到光的水,會變得比遮蔽區的水要熱一些,這個溫差就會讓水變得不均勻,影響成像。為了避免溫差,必須讓水快速流動混合,但又可能會產生漩渦。

「這很考驗我們機台放水的裝置,如何讓水流快速均勻又不起漩渦?這是個大學問,至今放水裝置起碼重新設計了六到八次。」

水的另一個特點,就是「它是很好的清洗劑。」林本堅說。在使用浸潤式微影技術時,水很容易把鏡頭等所有接觸到的東西上的雜質都洗下來,「結果就是晶圓上有上千個缺陷(defects)。我們花了很多功夫把缺陷的數量從幾千個,降到幾百個、幾十個,最後降到零。」林本堅說:「那是需要投入很多人力和晶圓才能完成。」

半導體人才需要是專才、通才,也要是活才

演講的最後,身為清華大學半導體研究學院院長的林本堅提及人才的培養。半導體的技術已經演進到非常複雜的程度,沒有一個學生能精通所有的技術層面。林本堅說:「所以你會發現,半導體需要團隊互助合作。」

而踏入這塊領域的學生,林本堅期許除了要有基本的理工能力外,還需要有對問題的好奇心,會發現新問題,也會找到有趣的新技術(活才)。「如果不能自己發現新的技術,會永遠跟在別人後面。」

林本堅強調,這不是簡單的事情,因為「真的有學不完的東西。」半導體可以分成材料、製程、設計、元件四個領域,「我們希望學生至少在一個領域很精通,有本領深入鑽研(專才)。但對其它的領域,也得有某種程度的認識(通才),才能彼此合作,解決問題。」

註解

註1:DOF=k3λ/sin2(θ/2),k3 是因應高 NA 值的曝光鏡頭所引入之係數。

延伸閱讀

- 111 年知識饗宴——蔡元培院長科普講座「光學微影縮 IC 百萬倍」

- 張顏暉(2021)。〈半導體元件的發展與運用-做晶片到底有多難?〉,《科技大觀園》。

- 詹益仁(2020)。〈摩爾定律的華麗謝幕:EUV 微影機〉,《DIGITIMES》。

- 郭雅欣(2020)。〈微影製程再進化!複雜電路的祕密〉,《科技大觀園》。

- 林本堅(2019)。〈推進微影技術二十代〉,《科技大觀園》。

- 劉俊宏、余浩澐、蔡坤諭(2013)。〈讓摩爾定律成真的關鍵:微影技術——影響七十億以上個未來〉,臺大電機系科普新知。

- 黎瑛蕊(2013)。〈林本堅以浸潤式微影技術開創產業未來〉,《工業技術與資訊月刊》。

- Lin, B. J. (2019) “Innovating from History“, Proc. SPIE 10584, Novel Patterning Technologies 2018, 1058402.

- Pease, R. F., & Chou, S. Y. (2008). “Lithography and Other Patterning Techniques for Future Electronics“. Proceedings of the IEEE, 96(2), 248-270.

- Ulrich, W., Rostalski, H., & Hudyma, R. (2004). “Development of dioptric projection lenses for deep ultraviolet lithography at Carl Zeiss”. Journal of Micro/Nanolithography, MEMS, and MOEMS, 3(1).

- Lin, B. J. (2000). “New λ/NA scaling equations for resolution and depth-of-focus“, Proc. SPIE 4000, Optical Microlithography XIII.

- Nikon | Semiconductor Lithography Systems | Semiconductor Technology

- ASML EUV lithography systems

- Chip technology earns Japan Prize. IBM Research Blog.