文/喻守謙

2015 年國際「TOP500 計畫」在德國舉行的國際超級電腦大會上,發表全球最新超級電腦 500 強排名。雖然排名前端的超級電腦,皆已經可以達到每秒運算千兆次的速度,但事實上超級電腦計算能力成長的幅度並不像過去那麼快速,成長放緩的原因可能涉及許多技術難關及成本考量。

超級電腦還在成長,但成長的很慢

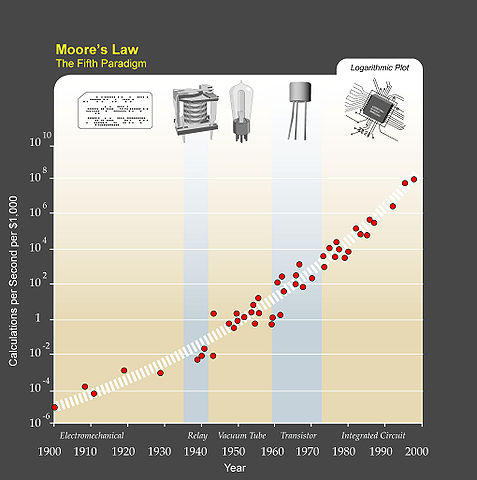

眾所皆知,超級電腦的開發根基於 INTEL 創始人之一戈登·摩爾所提出的摩爾定律,他預測單一積體電路上可容納的電晶體數目,約每隔2年便會增加一倍,造成性能呈指數增長。在大多數情況下,市場大多遵循著這套曲線。

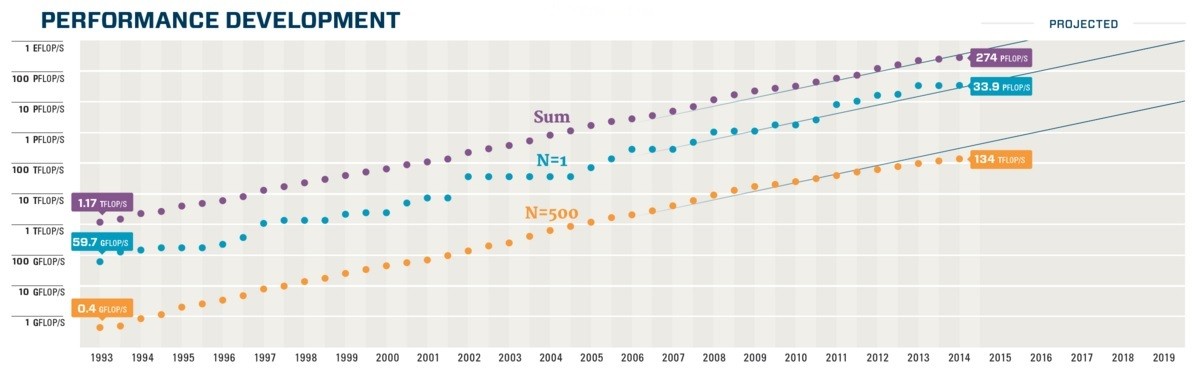

在超級電腦方面,過去前 500 強的電腦性能幾乎每年翻倍成長。然而從前幾年開始,成長的幅度漸漸下降。從 2008 年到 2013 年左右,運算速度增長的幅度約在 22%-66% 左右,但今年上榜的電腦中,只比去年同期增長了約 17% 左右。

成長的停滯跡像不只出現在榜單的頂部,榜單底部的電腦也有漸緩的趨勢。就過去的經驗來看,榜單底部的電腦處理速度的增幅應該要持續高於排名靠前的電腦。但從下圖中,我們可以看出在過去的幾年中增速的變化趨勢。排名第 1 和第 500 的電腦間運算能力差距正在逐漸擴大。

也就是說,雖然還是有新的超級電腦誕生,但出現的頻率已經沒有過去那麼高,且榜單底端的電腦也沒有維持足夠的成長速度。

甚麼趨勢導致成長放緩?

摩爾定律走到盡頭

IBM 數據中心高級經理 John Gunnels 提到,如果你沒辦法像過去一樣保持芯片縮小的幅度與速度,那麼當然沒辦法像過去一樣提高效能,因為晶元的幾何尺寸總不可能無限制地縮小下去。半導體產業似乎已經走到極限,今日的晶體管已經縮小到原子級別,芯片設計師們不得不在已十分優越的多核芯片上不斷推翻、重新設計,每一次的升級,都讓難度變得更大。於此同時,IBM 研究人員正試圖利用矽鍺晶體管取代純矽,並利用極紫外光(EUV)雕刻技術,打造僅 7 奈米的芯片,希望在未來四年維持摩爾定律。

除了純科學技術上的問題,更大的問題是經濟上的阻力,高昂的電力消費與天價的開發成本才是減緩相關產業成長的原因。當芯片對尺寸的要求縮小到一定程度,晶圓廠的成本甚至可能會高過核電廠,除了大型科技公司以外,恐怕沒有多少公司能負擔。例如 Intel 過去的 14 nm 晶片工廠,便花費了五十億美元,上述 IBM 的新型晶片,在量產前投資額就高達 30 億美元。Gunnels 認為,他相信有人能做出性能更高的超級電腦,但不見得有相對應的權力與金錢能夠支撐這項事業,例如美國政府近年來也縮小了對超級電腦的資金投資規模。

當然,除了一味追求更小的半導體體積外,市場上還有其他技術可以增加運算效率。如 3D 邏輯閘,多層晶片,低電壓低電阻晶圓等等,但這些技術也有自身的限制,沒辦法立即帶來像如同縮小體積般顯著的指數型成長,頂多讓半導體產業維繫接下來 10 年的光景。換句話說,科技巨頭們只能趕在這段時間去尋找能矽半導體的替代品,雖然有不少可能的方向,例如奈米碳管、超導體、量子電腦等等,但這些技術也都尚未完全成熟,是否真的能在近年扭轉頹勢,還有待觀察。

未來發展-你的舊電腦不再過氣的那麼快?

縱使成長放緩,美國科學界仍希望能在 2020 年達到每秒百萬兆次的運算速度,但田納西大學的電腦科學教授 Jack Dongarra(超級電腦前 500 名榜單中的常客)則認為保守估計也得等到 2023 年才能實現,日本與中國方面則較積極地想搶在 2020 達成這項目標。

在未來,首要受到影響的就是需要動用超級電腦的產業,例如國家級的氣象預測與氣候模型架構、新世代的雲端產業網路架構等等。對一般民眾而言,過去我們已經習慣芯片的高速淘汰與成長,未來或許也會開始查覺到這波放緩的趨勢,簡單來說,你會發現你的舊電腦似乎不會過氣的那麼快。

(本文由科技部補助「新媒體科普傳播實作計畫-智慧生活與前沿科技科普知識教育推廣」執行團隊撰稿)

責任編輯:鄭國威

審校:陳妤寧