在 AI 時代,傳統靠「電」傳輸的技術遭遇瓶頸,導致 GPU 效能發揮不到兩成。科技界為此祭出「矽光子與 CPO」黑科技,將晶片的「大腦(運算晶片)」與「眼睛(光學元件)」完美結合。然而,若封裝後才發現這些「光學眼睛」出現故障,恐讓價值數千美金的晶片大腦一起陪葬報廢!本文將帶您輕鬆讀懂這項引領未來的技術,看工程師克服重重困難,打通AI量產的最後一哩路!

本文轉載自宜特小學堂〈別讓昂貴ASIC陪葬!掌握矽光子KGD驗證關鍵,打通CPO量產最後一哩路〉,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

NVIDIA 黃仁勳預期 2027 年 AI 基礎設施將達兆元規模,但傳輸瓶頸導致 GPU 使用率低於 20%。為突破限制,NVIDIA 與台積電積極佈局 CPO(共同封裝光學),透過 COUPE 技術實現光電 3D 異質整合,預計 2026 年邁入量產元年。

然而,從「電」轉「光」是全新的戰場。工程師面臨的不只是漏電,更是漏光、光耦合偏差與訊號衰減等棘手失效。當設計走向實體產品,最關鍵的挑戰,便是如何透過嚴謹的驗證,確保這項高價值技術的可靠度與壽命。

之前我們已從矽光子元件組成與決定效能的關鍵(閱讀更多:「光」革新突破半導體極限 矽光子晶片即將上陣),進而分享對應的解決方案(閱讀更多:矽光子開發為何這麼難?驗證手法是關鍵),以及如何突破矽光子量產的核心難關(閱讀更多:矽光子CPO量產見曙光!從「漏電」到「漏光」如何迎刃而解?)。

本文將繼續帶領IC工程師轉換視角,從看診電性晶片的「神經內科醫生」變身為治療矽光子疾病的「眼科醫生」。我們將針對光子積體電路(PIC)的五大關鍵部件,詳細剖析其操作原理、常見故障模式以及尖端的故障分析(Failure Analysis, FA)技術,協助產業界打通矽光子量產的任督二脈。

一、把大腦跟眼睛包在一起:什麼是 CPO?

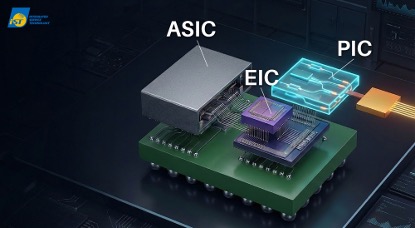

CPO(共同封裝光學)的核心概念,是將原本獨立的光收發模組與高階交換器晶片(或運算晶片)整合在同一個封裝載板上,大幅縮短電訊號傳輸距離,進而降低功耗與延遲。簡單來說,就是把晶片的「大腦」跟「眼睛」裝在同一個小盒子裡。在這個架構下有三個核心好夥伴:

- ASIC(大腦):負責高階運算的系統大腦。

- EIC(神經橋樑):負責放大訊號,擔任大腦與眼睛之間的翻譯官。

- PIC(眼睛):負責把電訊號變成光,用光速把資訊傳遞出去。

這種「異質整合」把大家拉得非常近,可以大幅降低延遲和功耗,但也帶來極大的「光電整合」的品質挑戰。

二、光學晶片的5 大嬌貴器官(PIC)與常見「疾病」

相較於業界已熟稔的 ASIC 與 EIC電路故障模式,PIC (光路) 才是CPO驗證中最陌生的戰場。PIC 這個光學元件裡面有五個關鍵部位,它們各有各的脾氣,如果生病了就會引發大災難;要精準定位並排除這些微觀病灶,極為仰賴尖端的故障分析(FA)技術,才能在量產前完成最後的風險收斂。

- 光柵耦合器 (Grating Couplers, GC) :

「光的專屬漏斗」,負責讓外部的光精準進入晶片。 對位只要稍微偏一點點,或是掉進一顆小灰塵,光就會漏掉。

宜特實驗室可透過掃描式電子顯微鏡(SEM)、能量色散X射線光譜儀(EDX)、聚焦離子束(FIB)與穿透式電子顯微鏡(TEM),進行微觀缺陷分析,並透過切片檢查確認雷射與光柵耦合的實體完整性。

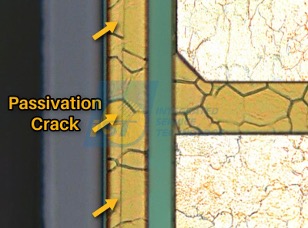

- 光波導 (Waveguides, WG) :

可說是「光的高速公路」,讓光在晶片裡奔跑的專屬通道。如果通道牆壁不夠平滑(側壁粗糙),光在奔跑時就會一直撞壁散失掉。

宜特科技可透過精細的切片分析(Cross-section),以觀察波導傳輸通道的結構尺寸是否合乎設計,並檢視是否有導致光訊號散失的結構變異或缺陷。

- 熱調諧器 (Heaters) :

可說是「溫度調節器」,透過加熱來改變光的特性。但很容易因為和其他元件靠太近而漏電,或是被靜電(ESD)打到直接燒毀。宜特實驗室針對漏電點進行橫截面檢查,並配合精密層次去除 (Delayer) 分析,逐層尋找燒毀或漏電的確切位置。

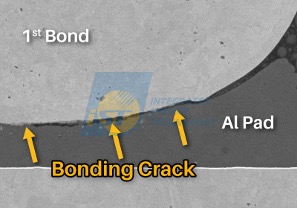

- PN接面調變器 (PN Junction Modulator) :

就像是「摩斯密碼發報機」,負責把電腦的「0 與 1」電訊號,變成「亮與暗」的光訊號。但偏偏它非常怕熱,溫度太高就會引發「熱飄移」導致失效,或者被靜電永久擊穿。

在宜特科技實驗室中,可透過掃描電容顯微鏡(SCM)或原子力顯微鏡(AFM),將載子濃度與摻雜輪廓具象化,以確認是否符合原始設計。當然,PN 接面的切片檢查也是不可或缺的一環。

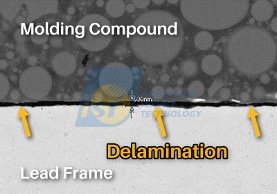

- 鍺光電偵測器 (Ge Photodiodes, PD) :

可想像成是「光的終點接收站」,負責在終點把「光」變回「電」。最致命的傷叫做「暗電流」(明明沒光卻偷偷漏電),這通常是因為材料裡混進了金或鋁等金屬微粒污染造成的。

鍺光電偵測器的分析極具挑戰性。宜特科技透過電子束誘發電流(EBIC)技術進行高解析度的電性故障定位,再輔以穿透式電子顯微鏡(TEM)、能量色散X射線光譜儀(EDX)以及二次離子質譜儀(SIMS)進行深度的晶格缺陷與金屬污染分析,確保找出導致鍺光電偵測器失效的真兇。

三、為什麼量產這麼難?工程師面臨的終極大魔王

當這些技術要真正做成產品賣到市場上時,會遇到兩個超可怕的陷阱:

- 大魔王一:「盲人穿針」的對準難題:

要把光順利打進比「頭髮還要細」的通道裡,誤差必須小於 0.5 微米。這就像是矇著眼睛穿針線,非常耗時,嚴重拖慢了產品出廠的速度。

- 大魔王二:「一顆老鼠屎壞了一鍋粥」的陷阱:

因為 CPO 技術是把便宜的光學小零件,跟價值高達數千美金的 AI 大腦(ASIC)封裝死在一起。如果便宜的光學零件壞了,而且是在封裝後才發現,那整顆昂貴的 AI 晶片就只能直接當垃圾丟掉,這會讓公司的利潤瞬間歸零。

四、 解決方案:幫晶片做全套的「健康檢查」

為了解決這個把昂貴晶片陪葬的風險,業界現在採用了一套非常嚴格的標準(例如 Telcordia GR-468)。從晶圓剛出生的嬰兒期(Level 1)到最後組裝完成的成年期(Level 5),都要進行非常精密的「定性與定量」動態健康監測。

只要能精準掌握這些微小的病灶,找出漏光、漏電的真兇,我們就能打通這項技術的最後一哩路,迎來速度更快、更省電的AI新世代!

本文出自 www.istgroup.com。