本文轉載自宜特小學堂〈矽光子開發為何這麼難?驗證手法是關鍵〉,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

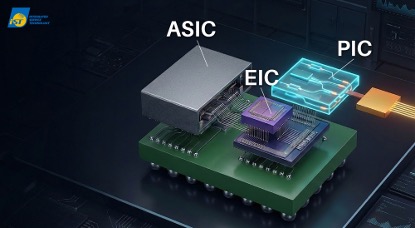

談到「漏電」,你一定很熟悉;但「漏光」呢?在積體電路(Electrical Integrated Circuit, 簡稱EIC)的世界,短路、開路、金屬遷移,是工程師每天要面對的課題。然而,當「光」也被整合進晶片,遊戲規則就完全不同了。

在矽光子積體光路((Photonic Integrated Circuit, 簡稱PIC)的世界,要處理的不是電子,而是光子:耦合損耗、波導裂縫、散射與吸收,都可能成為隱形殺手。你不再只檢查電流是否順利通過,而是要量測不同波長下的衰減(Insertion Loss)、偏振依賴性(PDL),甚至追蹤隱藏在波導裡的漏光點。

在邁向 CPO(Co-Packaged Optics,共同封裝光學)的道路上,幾乎所有研發團隊都深有同感:前一步才剛突破設計,下一步卻又卡在測試或封裝。從漏光、光損,到可靠度與良率,每個環節出錯都可能拖慢你的進度。

矽光子開發為何卡關?

從宜特實際接案經驗來看,依照製程順序,可歸納出五大痛點:

- PIC 前段驗證不足:

由於缺乏PIC晶片封裝前的 Pre-test 介面,加上 Die-to-Die 對位精度難以掌握,往往導致後段整合良率下降。

- 光學元件可靠度驗證難以量化:

目前矽光子產品在可靠度驗證上存在兩大挑戰:一是光電二極體(Photodiode, PD,光檢測器)缺乏可程控、多通道的老化測試平台,導致其在高功率或長時間操作下的壽命特性難以量化;二是光學元件在進行溫度循環、濕熱、震動或灰塵等可靠度試驗時,對於Insertion Loss(IL,光損耗或插入損耗)的變化缺乏明確數據,也讓研發團隊在長期可靠度驗證上面臨更大風險。

- 晶片切割(Die Saw)s風險高:

對於 Low-K 材料的 PIC 晶片而言,切割過程容易產生邊緣崩裂(chipping)與結構損傷,影響後續的可靠度與性能。

- 缺陷分析與 CP 測試困難:

光損熱點與漏光位置難以快速定位,而波導、耦合器、調變器等結構缺陷的分析亦缺乏精準工具。

- CPO 封裝挑戰嚴峻:

在 PIC、EIC 與 FAU (Fiber Array Unit) 的組裝過程中,封裝翹曲(warpage)問題常導致良率降低,成為工程師迫切需要突破的瓶頸。以上這些問題,宜特早已準備好解答。從 Substrate/Socket 設計、光及電測試、可靠度驗證、結構分析,我們都可提供標準化、可擴充的測試方案,完整支援你的矽光子開發流程。

Q1:PIC 在封裝前要怎麼測?沒有介面怎麼辦?

A1:很多團隊因為缺乏 Pre-test 介面,只能等到正式封裝後才知道結果,風險很大。宜特能設計客製化 Substrate 與 Chip Bonding 流程,支援晶片在封裝前就能進行高速光測試;同時透過精準 Die-to-Die 對位,幫助工程師在驗證階段就把握良率關鍵。

Q2:光檢測器(PD)怎麼模擬高功率與長期使用情境?

A2:多數客戶苦於沒有多通道、可程控的平台,無法進行長期老化測試。宜特打造定電流、定電壓模組,可同時測試多組PD。可程控雷射源,模擬高功率工作環境。並能提供完整的長期壽命驗證,針對光老化、PD stress 提供完整解決方案,確保 PD 元件的穩定度。

Q3:光學元件的可靠度要怎麼量化?IL 變化沒有標準依據怎麼辦?

A3:在溫度循環、濕熱、震動或落塵等可靠度測試中,IL 變化往往難以界定。宜特建立了全系列可靠度測試流程(TCT、熱循環、震動、落塵…),並以 IL 變化作為Pass/Fail判斷,讓風險數據化,設計決策更有依據。

Q4:遇到光損熱點或波導缺陷,該如何快速找到問題?

A4:傳統檢測常像「黑盒子」,缺陷難以被精準定位。宜特與光晶片量測設備商光焱展開合作,導入Enlitech NightJar光學檢測平台,透過晶圓層級光損 mapping,不只能找到漏光位置,此平台更能量化光衰數值並精準定位異常區域。同時,我們也能針對耦合器、波導、調變器與 PD 進行深度結構分析,完全攤開隱藏缺陷。

Q5:CPO 封裝與晶片切割最怕良率掉,該怎麼避免?

A5:PIC + EIC + FAU 的組裝常因封裝翹曲(warpage) 而降低良率。宜特提供組裝前 Warpage 量測,在問題放大前預防風險。另外針對 Low-K PIC 晶片切割,我們具備雷射溝槽(Laser Grooving)和精密刀片切割(Blade Dicing,簡稱BD)技術,有效降低邊緣崩裂(chipping),提升晶片良率與可靠度。

少走彎路,才能快一步從電路跨向光路

隨著 AI 伺服器與高速交換器需求飆升,業界將加速導入 CPO(Co-Packaged Optics)與光電整合 (EIC+PIC) 的應用。宜特矽光子驗證一站式解決方案,從設計、光電測試、可靠度驗證到封裝挑戰,不僅協助你縮短研發時程,更確保每一步都有數據依據,少走彎路。