張峯鳴 (FM Chang) 一定很想知道,這篇訪問的 ROI (投資報酬率) 好不好?能不能真的幫上學弟妹?

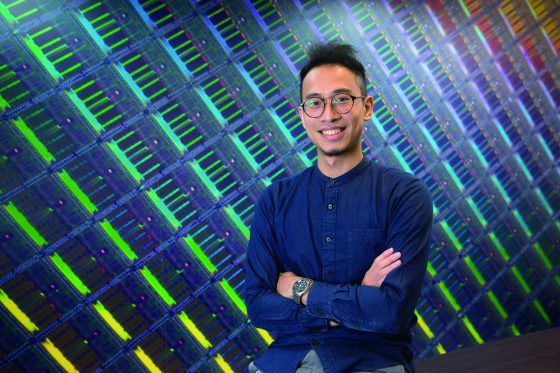

身為跨國半導體大廠德州儀器 (Texas Instruments, 簡稱 TI) 產品測試部門經理,擔任管理職同時又具有 “Technical Ladder” 身份 (也就是德儀認定之技術專家) 的張峯鳴,看起來十分年輕,剛成為新手爸爸的他,研究所畢業後已經在德儀任職近八年,但採訪此刻看起來被認成大學生也不奇怪。在這泛科學一年一度的職涯專題中,我們邀請跟泛科學許多讀者背景相似的他來聊聊自己的求學經歷與職涯探索過程。

理科集大成:太空人的夢、會計師的腦、物理人的心

「說來有點好笑,我小時候很想當太空人。」張峯鳴還記得上小學前最初的職涯想像。他說,除了覺得太空人穿著「機械感」十足,很帥以外,印象中小時候常常從電視新聞上注意到跟宇宙天文相關的消息。

「媽媽可能還在幫我擦鼻涕,爸爸看的電視新聞裡大多都是政治人物吵來吵去,但只要有類似哈伯望遠鏡發現了什麼什麼的消息,我就覺得感興趣,認為自己聽得懂。」他說。

到了國中,媽媽送他去參加成功大學的航太營,由航太系學生帶領,接觸各類機械、構造。僅管其他學員年紀比他大,有點邊緣的他還是覺得「超好玩」。他說在營隊裡,能將學校教的牛頓力學實作展現,各種水火箭炫技玩法讓他不亦樂乎,大學生哥哥姊姊們示範的高空落「蛋」,也讓他躍躍欲試。

儘管高中時對天文太空依舊興趣滿滿,他說「可能是 ROI 的概念在我心中萌芽了,就越來越實際了。」他很清楚自己對理工科感興趣,但也納悶:熱門的志願怎麼都沒有航太、天文?他發現相關的知識領域在物理系裡都有,所以升大學填志願時選了多所大學的物理系,最後則在熱門跟理想志願之間折衷,成為清大動力機械工程學系的新生。

為何不選出路看似更明確的電機系?其實原本是三類組的他,家裡長輩也曾勸他選醫科,但他很有主見,想把物理學好,他記得高中時心裡想:「難道唸電機未來就是修手機、念機械就是修車嗎?還是不要先決定修什麼好了,先念物理!」

上大學後,張峯鳴視野大開,認識的人一下子多了起來。同學關心的事情不只是學業、還關心環境議題、社會服務等,享受且渴望新刺激的他,便找機會出國交換。到美國密西根州立大學那段時間,更讓他看到台美兩地學習方式的差異。

「他們看待跟處理事情的方式跟台灣很不一樣。他們很歡迎多元人才,所以入學不難,但淘汰不夠格的人卻毫不手軟。」他表示當時他同時選修開給大一到大四的課程,在大一生比較多的課堂上,不少人有來玩玩的感覺,功課討論起來愛做不做;但到了大四為主的課程就超精實,剩下的每個人都很清楚自己要什麼、都想在專業領域上有好成績。「感覺他們在大學每一年越來越強。有種修煉的感覺。」

比較之下,他覺得在台灣念大學,最難的是「考進大學」,很多人有上大學之後被當也沒關係的想法。而在美國不管是不是基礎課程,實作都很多。「會讓你每天都很忙,但很有收穫,所以回台灣之後我就選修這樣的課。」

最划算的選擇:如何出國學經驗、練英文、又不花錢?

基於出國交換時的深刻體驗,他本來打算出國讀研究所,也趁機玩一遭,但這想法被自己推翻。他是個在決策前總是會做好一番分析的人,不管是該不該出國讀研究所、或是要不要接受一次採訪。考慮家境與對未來理想人生的想像後,他認為在台灣唸研究所更省時間跟成本,以後想出國玩還有機會。

在台大唸電機研究所時,他參加了校內的就業博覽會,在德州儀器的攤位上,得知這家公司有 New College Graduates 科技菁英培訓計畫,雙眼為之一亮!這是德儀為剛畢業的學士或碩士,或是工作未滿一年的職場新鮮人量身打造的培訓計畫,為期 18-24 個月,涵括七大面向,從產品技術、專案管理、影響力建立、公司文化、處理訂單、報價交貨,到向高階技術主管、各國主管直接學習,並獲得回饋。此外,還能輪調到世界各地,一邊練英文、增加國外經驗,又不花自己的時間跟金錢。這完全擊中了張峯鳴的甜蜜點,於是畢業後就立刻加入德儀。

「當然啦,還是有很多工作要做。」很在乎名實相符的他,雖然受「菁英輪調計畫」吸引加入公司,但也坦言當初蠻不喜歡這計畫的名稱,畢竟當時覺得自己很嫩,不想被戴高帽子,但他後來卻紮實地透過這計畫讓自己成為名實相符的菁英。他每年輪調,接受不同訓練,從測試、品管到美國總部晶圓廠服務,逐步增進對公司與全產業的了解,提高了跨部門合作的能力。2015 年,德儀決定進入高壓電 IC 市場,張峯鳴扛起重任,從無到有,將台灣生產線建立起來,過程中與美國同仁合作開發技術,極為傑出的表現,更讓他受遴選成為公司認可的技術專家 Technical Ladder 一員。

Technical Ladder 直譯為「技術階梯」,其實是德儀為研發人員設計的升遷制度。Technical Ladder 分三層,在不同的層級有不同的競爭。因有比例限制,各廠要派出高手去跟他廠比賽,才能獲得此高榮譽職銜,並獲得薪資加給跟專業認可。「在這裡工作,大家都有企圖心,但不是每個人都適合領導或都有朝管理職發展的想法,因此可以朝技術專家的方向走,薪資跟職位一樣可以繼續提升,不會因為非管理職就停留在原本的位置。」儘管如此,張峯鳴卻身兼 Technical Ladder 一員與部門經理,可見他自己設定的階梯更具挑戰性。「能力跟國際觀的培養真的很扎實。loading 雖然重,但成就感也很強。」他說。

雖然隨著工作年資增加,大學跟研究所時學的專業技術能用上的頻率越來越少,但科學思維卻潛移默化成他的處事邏輯;他十分感謝大學階段時遇見的清大王訓忠教授,讓他在上工程數學跟流體力學時收穫滿滿,更讓他愛上應用理論解決真實問題。「今天遇到一個問題,我會用流體的特性、機械熱應力的狀況去推測,更快找到解決方向。另外,在管理以及跟同仁相處時,我也常從生物跟生態學思考,如何讓大家能各取所需,讓每個人待在適合的區位,他們也比較有安全感。」他說。

科技一點也不難:在德州儀器,溝通和多元並進

許多人無法跟領域外的人「科普」自己的工作在幹嘛,包括對自己的爸媽。張峯鳴對此倒不覺得難,他說:「德州儀器就是做 IC,做得非常非常小,放在手機裡、車子裡、冷氣裡。像是你手機的放電跟充電就有一個 IC 在控制,電快沒了進入省電模式就要放少一點。」他補充,德儀人有一種共同特質,就是想讓人聽懂生冷的技術,而出現此般特質背後有兩個原因,第一是因為德儀規模大,座落在很多國家。第二,他認為,則是因為公司積極倡導合作精神,常需要跨部門合作,溝通成日常工作必備,更需要與財務部、採購部門等非科技背景、非技術部門的同事溝通,若「不講人話」絕對走不通。

許多公司隨著組織擴大,無可避免地染上大組織病,使得創新點子如死水停滯、溝通上下前後到處卡,德儀為了避免這樣的問題,全力倡導分享精神,更希望用組織規模來提高效率。張峯鳴說德儀鼓勵 “Innovate once, Implement everywhere” (一處創新、處處運用):例如在台灣做了嘗試,發現省了成本、增加效率,就要提供方法給其他國家的廠來複製,所以生產端很重視分享知識的方式。此外,「公司內部有論壇,好想法丟出去,就會有人接球。雖然上司在看但不會有壓力,他反而會對你的活躍表現讚譽有加。」

而身為有點典型的理工男,他認為在德儀的女性工程師專業表現不亞於男性,推動團隊往目標前進的能力卻更強,例如當部門間合作比較不順時,女性工程師往往能讓事情破冰。他也發現育嬰留停回來之後的女同事,做事變得更有效率,判斷更準確。「可能是因為家庭讓他們時間控管得更緊。重要的是,其他同事都願意配合。」現實生活中剛成為新手爸爸的他認為:「假若我是新手媽媽,我會繼續工作,至少在德州儀器,大家尊重性別之間的差異,也享受多元帶來的優勢。」

致年輕的自己:多實習,然後不要著急

雖然職涯順利開展,在工作裡獲得高成就感,但如果能夠回到過去,張峯鳴還是有些想修正之處。

他說:「推甄上研究所之後,覺得從小到大一直念書念下來好累,所以那時就保留學籍先當兵,退伍後大腦彷彿掏空,覺得知識好寶貴、很渴望學習。」不過,雖然他對這決定(先去當兵)蠻滿意的,他現在覺得應該要暫停更久一點,先去業界工作個幾年,這樣會更知道自己需要、欠缺什麼,更善加利用研究所的兩年。另外,對做任何事的成本跟效率非常認真看待的他,也強烈建議大學生多到業界實習,他說:「短短兩個月就能夠知道自己以後是不是要花十年在這裡面,非常划算。多去實習,對跨出職場的第一步更有信心。」

他代表過公司到大學招募實習生,他認為一來到德儀實習薪資不錯,二來能會接觸到正職的工作。更重要的是,由於各部門同時招收,同一批實習生會一起籌辦活動,例如計畫結束後的發表會,彼此會很熟悉,這樣一來能認識很多來自不同領域、但都很有熱情的人才,而且德儀若評估是需要的人才,就會直接發 offer,對公司來說也能降低雇用錯人的成本。「真是蠻超值的。」然而,他也強調來申請實習前,要清楚自己的目標,而不是「來看看」。

在訪問結束前,他最後想給現在正在思索職涯的學弟妹一個關鍵建議:「不要急。」

他感同身受地說,看到身邊的人上了什麼研究所、或是拿到了哪間公司 offer,可能會逼自己要趕快往某條路鑽,但其實可以給自己一些時間,好好想自己想做什麼。「不要像在台北車站下了捷運被人群擠著前進到錯誤的出口。」雖然他在這次訪談中給了許多誠懇的建議,但他更希望學弟妹能自己想清楚,這最重要。

既然那麼重視 ROI 的他都這樣說了,肯定是很重要的建議。你說是嗎?

本文由德州儀器與泛科技共同企劃