欒丕綱/清華大學物理博士,中央大學光電系副教授。研究專長為光子晶體,聲子晶體,以及超穎材料。

有沒有能夠抓住光,卻不消滅光子的方法?光子晶體不僅能讓光轉彎,還能讓動物展現美麗的色彩!

1980 年代時,人類對於光的認識已經很深入。那時人們已懂得使用透鏡組件,藉由改變折射率與介質表面的特定形狀以控制光線的傳播方向,如使用望遠鏡觀察宇宙,製作顯微鏡觀察微生物。

人們知道單一頻率的光通過雙狹縫會有干涉現象,而光波通過小尺度的物體會產生繞射與散射。利用光從「密介質(折射率大的介質)」傳向「疏介質(折射率小的介質)」,入射角大於「臨界角」時會發生的全反射現象,可以設計出波束分離器(beam splitter)、波導(waveguide),與光纖。利用光是電磁波的事實,可以藉著控制光的偏振與相位做出光學波片(wave plate)、濾波器,以及調制器 (modulator)。利用量子力學與半導體物理的知識,人們知道如何操控光子與原子的交互作用,製造出所需要的雷射以供進一步應用。

以上這些控制手段似乎缺少了什麼?仔細觀察,會發現這些對光的控制手段可歸納為以下幾種:(一)控制光的傳播方向,(二)控制光的傳播區域/ 範圍,(三)控制光的強度,(四)控制光波的相位與偏振,(五)控制光的相位一致性以及傳播方向的準確度。以上這些控制手段的共同特色就是「不能阻止光的傳播」。雖然光子可以被原子吸收或放射出來,但若試圖阻止光的傳播,那麼光子只能藉著被材料吸收而消失,轉換為其他能量,例如熱能。

光子晶體的發想

1987 年左右,雅布羅諾維奇(Eli Yablonovitch)與約翰(Sajeev John)兩位科學家不約而同地思考著阻止光傳播卻不消滅光子的可能性。

雅布羅諾維奇是一位實驗物理學家,曾任職貝爾通信研究所(Bell Communications Research)的研究員。他當時思考的問題主要是如何抑制原子的「自發輻射(spontaneous emission)」以減少能量的浪費,並增加雷射的效率。根據雅布羅諾維奇教授的回憶,當時曾有一些研究者建議將發光的原子置於「兩面金屬牆」之間;另一些研究者則建議使用「一維布拉格光柵(1D Bragg grating)」以取代金屬牆。然而,雅布羅諾維奇博士認為這兩種方法都行不通。

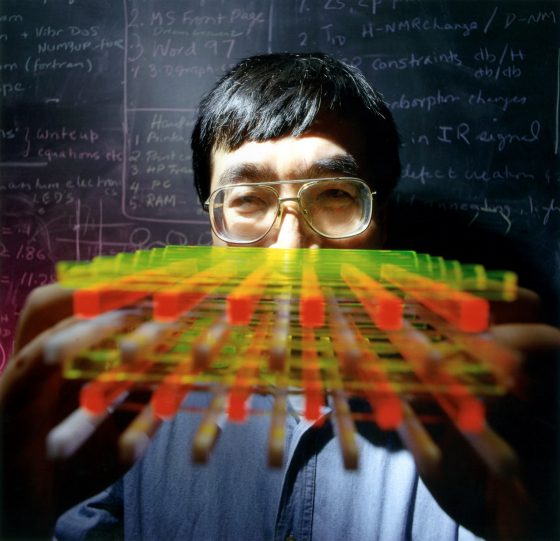

第一種方法只能阻擋某一種偏振的光,因此只有一半的效果。另一種方法雖然能阻擋朝著布拉格光柵週期方向傳播的光,但是對於朝著垂直於週期方向(此方向介質是均勻的)傳播的光卻沒有效果。雅布羅諾維奇於是試著在紙上畫出他認為行得通的三維週期結構,並在往後的幾年中不停試著對介電質鑽洞,以找出確實可行的週期結構。經過了好幾年的失敗,並在跟理論物理學家的合作下,在鑽了大約五十萬個洞之後,終於找出了理想可行的三維週期結構。

另一位光子晶體概念的提出者約翰,則是基於完全不同的理由而提出這個概念。約翰是一位理論物理學家,那時的他是一位普林斯頓大學(Princeton University)的年輕助理教授。當時他所思考的問題是,如何讓光在介質中的傳播停下來。

故事先回到1958 年,當年服務於貝爾實驗室(Bell Labs)的凝態物理學家(condensed matter physicist) 安德森(P. W. Anderson,1977年諾貝爾物理獎得主)從理論上發現了一個很驚人的現象,後來被稱作安德森局域化(Anderson localization):在一個充滿隨機分布的雜亂位能(random potential)的材料裡,電子可以因「多重散射(multiple scattering)」而被困在其中無法移動。根據量子力學,支配電子的各種行為的是薛丁格方程式(Schrödinger equation)─ ─ 這是一個波方程式(wave equation),因此安德森局域化現象其實是一個波現象,與電子的粒子性似乎並沒有直接關係。科學家們理解到這一點後,忍不住好奇的問:這樣奇特的波現象會不會也發生在光波與聲波系統?如果有,能不能觀察到?

約翰的博士論文所研究的就是局域化現象,因此他對於安德森局域化的理論內涵有很深的理解與掌握。對應於電子系統的隨機位能,在光學系統內所要準備的是具有隨機分布的凌亂折射率的透明介質。然而,研究者發現,理論上要達到把光完全困住的結果,所需要的介質樣品必須非常大,而且在實驗上很不容易把這個現象,與光在傳播過程中介質對光能量的逐步吸收效應區分出來。約翰於是建議先做出週期性的介質,再將介質的週期稍微弄亂一些,如此在某些頻段就可以用較小的介質樣品將光完全困住。

雅布羅諾維奇與約翰目前分別是加州大學柏克萊分校(University of California, Berkeley)與加拿大多倫多大學(University of Toronto)的教授。根據雅布羅諾維奇的說法,當年他們在學術界頂級的物理期刊《物理評論通訊》(Physical Review Letters)各自發表了他們的第一篇光子晶體研究論文,兩篇論文的刊登日期相隔不到一個月。當他們聽說了彼此獨立提出了相似的研究概念後,就相約吃午飯,並一起為這個概念取名為光子晶體(Photonic Crystals)。

現今看來,這個既含有「光子」又含有「晶體」的名字取得十分誘人。這個說法從每年有眾多光子晶體相關的研究論文被發表就可以看得出來。另一個觀察指標則可以簡單地經由Google搜尋查到,這兩位先驅的第一篇光子晶體論文目前分別累積了13725次與9582次引用次數。不過,在論文發表後,他們的論文並未立刻引起其他研究者注意。事實上,雅布羅諾維奇此論文發表後的頭三年,完全沒有其他人引用,前五年也只被引用兩次,而且這兩次還都是雅布羅諾維奇教授自己引用的。然而,進入90年代後,半導體製程技術的進步使得人們很容易製作尺寸從數百奈米至數微米的週期結構,而電腦運算資源的大幅成長,也讓人們很容易從理論上去計算出所設計的光子晶體的光學特性。這兩方面的重要發展促使了光子晶體的研究無論在數量與速度上,都以指數函數的方式隨時間成長。

光子晶體基本性質

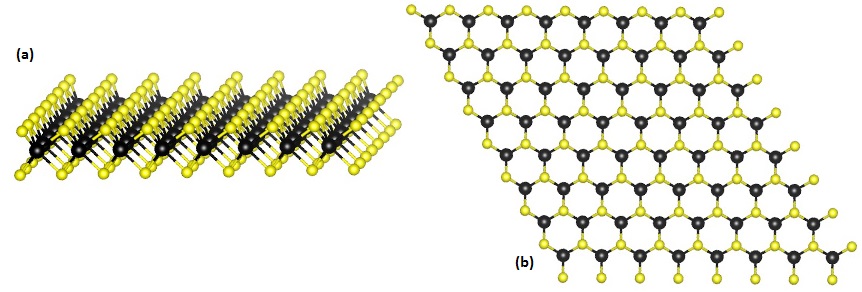

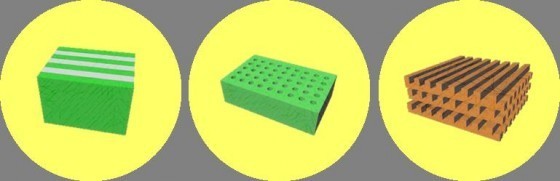

講了那麼多故事後,那麼到底光子晶體的定義是什麼呢?背後的物理原理為何?所謂的光子晶體,其實就是「介電質的週期結構(periodic structure of dielectrics)」。

所謂介電質(dielectrics),即非金屬的材料;而所謂週期結構,就是在空間上無窮次重複的圖樣(repeat patterns)。化學課本告訴我們:「完美的固態晶體具有週期性的原子排列」。光子晶體的週期結構就像那樣,只不過光子晶體是將晶體中的原子以介電質的「人工原子」取代,尺寸也較真實晶體放大了數十倍甚至是數百倍。另外,在普通的半導體晶體物質中,導電須依靠電子通過週期性的位能;而在光子晶體中,光傳播是靠光波通過具有週期性變化的介電常數/折射率的介電質材料。

在半導體的研究中,人們很早就知道,週期位能對電子傳播的影響就是產生了能帶結構(energy band structure)與能隙(energy band gaps),後者又稱禁制帶(forbidden bands)。也就是說,可以在半導體中傳導的電子,它們的能量分布是一段一段的,而這每一段被稱為一個能帶。與此類似,在光子晶體中可傳播的光,其頻率的分布也是一段一段的,每一段稱為一個「頻帶(frequency band)」。夾在相鄰的兩個頻帶之間的則是頻隙(frequency band gaps) 或帶隙。根據量子力學,光子的能量與它的振動頻率成正比,比例常數是普朗克常數h,因此我們也稱光子頻隙為光子能隙。

光子頻隙

為何會出現頻隙? 這不是個容易回答的問題。此處提供一個比較直覺的看法。當光波在週期結構中傳播時,會經歷多重散射,散射後的各分波與入射波一起疊加成總波場。這些分波疊加後在空間中形成建設性干涉與破壞性干涉的許多區域。在二維與三維的世界裡,破壞性干涉的區域若是形成各自分離的「孤島」,波能量仍可藉由連通的建設性干涉區,繞過這些孤島而傳播。反之,當建設性干涉的區域彼此互不相連,它們自己形成孤島時,波能量將無法傳遞。若在一整段頻率範圍內波能量都無法傳遞,則這一段頻率範圍就形成頻隙。

以上雖然說明了頻隙是波的一種破壞性干涉的效應,但很難從直覺上看出這個結果。頻隙可以很容易藉著不算太複雜的數值方法以電腦程式計算出來,但是幾乎不可能僅僅藉著用筆就推導出它在頻率軸上的正確位置與寬度。

光子晶體的應用

設計出這種有頻隙的光波介質,除了能將光波擋住,讓它傳播不了以外,有什麼積極性的應用嗎?答案是:有的。

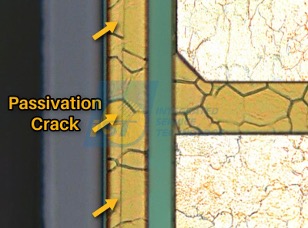

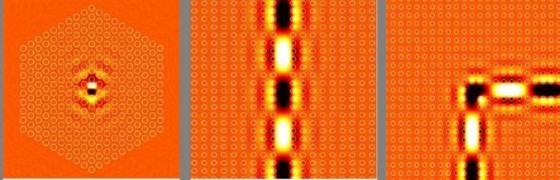

通常用來製造光子晶體的方法,就是在一塊完整的介電質上周期性的打洞,或是用許多介電質小球或介電質柱子排成週期結構。利用光子晶體的頻隙特性,只要選擇將週期性做局部的破壞,就可以製造出許多有用的奈米光學元件。例如在介電質中製造「點缺陷(point defect,基本方法是在某一個該打洞的位置不打洞)」或「線缺陷(line defect,少打一整排洞)」,就可以將光波侷限在該缺陷附近以形成「共振腔(resonant cavity)」或是「光子晶體波導」。

傳統波導是利用全反射將光侷限在波導中,若是波導的轉彎角度過大,全反射條件就會被破壞,導致漏光。然而,光子晶體波導藉由頻隙效應將光鎖在波導內,工作原理與全反射無關,因此可以大幅度改善傳統波導大角度轉彎的光能損耗問題,實現光迴路的微小化。這使得在小尺度製造出「積體光路」以取代傳統「積體電路」變得可行,換句話說,使用光子取代電子作為資訊傳輸與處理媒介的可能性將大幅提高。基於這種可能性,雅布羅諾維奇甚至在一篇介紹光子晶體的科普文章中,稱光子晶體為「光的半導體」。利用同樣的原理,也可以製造出橫截面是含有點缺陷與週期結構的光子晶體光纖,用以輔助或取代部分傳統光纖。

負折射應用

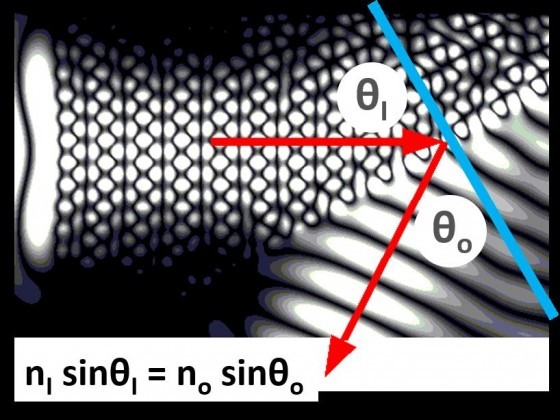

除了頻隙效應,光子晶體的傳導頻帶其實也有妙用。透過光子晶體頻帶所提供的特殊色散關係(dispersion relation),光波在某些頻率範圍內表現出不尋常的傳播行為。而其中最有趣的就是負折射。當光由真空進入介質中, 若折射波折向法線的同一邊, 則根據司乃爾定律(Snell’s law) 可定義此介質具有負的折射率。

目前至少有兩種方式可實現負折射。第一種是利用光子晶體在「頻帶邊緣」(band edge)的特殊色散關係製造出「負群指數」(negative group index),其類比於半導體能帶理論中電子的「負等效質量」(negative effective mass)。第二種方式是製造一種在每一個晶胞(unit cell)中包含有共振器(resonators)的金屬性光子晶體。適當選取頻率範圍,可使此介質的等效介電常數、磁導率以及折射率皆為負值。

2000年10月,倫敦帝國理工學院(Imperial College, London)的彭德里(J. B. Pendry)教授在《物理評論通訊》上發表一篇著名的文章,證明一塊折射率為-1的負折射介質板是一個「完美透鏡」,具有放大「消逝波(evanescent wave)」的神奇能力,可將波源「完美成像」而超越繞射極限。此文發表後,立即在學術界掀起了負折射研究的熱潮。在研究者的持續努力下,負折射的現象已證明確實存在,且Science 期刊基於其應用潛力(例如新式的讀寫頭等),將相關研究選為2003 年的十大科技成果之一。更有甚者,這方面的研究後來重新取了一個名字,現在被稱「超材料」或「超穎材料」,是當前最熱門的研究領域之一。超材料研究目前最受矚目的研究方向是可超越繞射極限的超級透鏡,以及可以將物體隱藏起來的隱形斗篷。這兩方面的報導常可在新聞中看到。具體的細節可以參考筆者從前寫的一篇文章。

上述各種研究所談的都是光波或電磁波,但其實聲波或彈性波的特性與電磁波非常類似,可使用同樣的手法處理。藉著製造週期性的彈性材料,例如週期性的混搭兩種彈性係數與質量密度不同的材料,也可以製造出「聲子晶體(phononic crystals,或稱 sonic crystals)」,像控制光波一樣地控制聲波與彈性波(例如使用頻隙效應做防震)。此外,若是把「聲波共振器」做週期性的排列,人們也可以做出聲波版本的超材料,可用以設計聲波版的超級透鏡或聲波斗篷。

上述的介紹或許會讓讀者以為這些能控制光的週期結構都是人造的,這個觀念其實錯了。現在科學家們已在許多生物的身上發現了光子晶體。簡單舉幾個常見的例子:孔雀的羽毛、蝴蝶的翅膀,以及變色龍的皮膚,都被發現隱藏著特定的週期結構。換句話說,光子晶體就是牠們得以美麗以及迅速變化偽裝的秘密。

光子晶體以及相關的聲子晶體以及超材料研究,在當前依然非常火熱。許多概念已經釐清,某些夢想已經實現,還有一些設計的元件已經有小幅度的商業化。本文只對光子晶體概念做了最粗淺的介紹,有許多近年來的重要發展,例如光子晶體在太陽能電池研究中的應用,都沒有辦法仔細介紹。有興趣的讀者可以試著從參考資料以及相關的網路資料中去進一步的尋找想知道與想學習的材料。

參考資料

- Yablonovitch, E., Photonic crystals: semiconductors of light, Sci Am., Vol. 285(6):47-51, 54-5., 2001.

- 欒丕綱,〈現代光學隱形術—從隱形斗篷到變換光學〉,《科學月刊》,508期,277 頁,2012年

- Teyssier, J. et al., Photonic crystals cause active colour change in chameleons, Nature Communications, Vol. 6: 6368, 2015.

延伸閱讀:

同步輻射光源解密

超短脈衝雷射改變世界

什麼?!你還不知道《科學月刊》,我們46歲囉!

入不惑之年還是可以當個科青