- 本文轉載自科技大觀園,原文為《氣候變遷、能源廢熱怎麼辦?——專訪國立陽明交通大學材料科學與工程學系吳欣潔教授》

- 作者 / 科技大觀園特約編輯|許君咏

在科技迅速發展的時代,加上溫室效應等因素,用電量逐年攀升,「電」成了人類社會中不可或缺的存在。然而,你知道嗎?各種能源產生的電力,有 60% 以廢熱形式逸散到大氣中,而真的拿來用的大約只有 40%。這些大量的廢熱也造成溫室效應加劇,其中工廠以及車輛引擎為能源廢熱的大宗。「氣候變遷」及「能源需求」兩大議題,逐漸形成彼此相扣的存在,究竟孰輕孰重,能否在這之中尋找一個平衡點,成為現今科學家們亟需解決的難題。

小孩子才做選擇,熱電材料:我都要!

「我常看著窗外想著,如果能把這些熱收集起來,拿來發電,是不是就同時能夠解決廢熱和氣候變遷的問題了?」吳欣潔教授說。

現為國立陽明交通大學材料科學與工程學系的吳欣潔教授,是今年 (2021)台灣傑出女科學家第十四屆新秀獎得主,近年來專注研究綠色能源的開發與應用,從熱力學探討至熱電材料。其實,吳教授在大學時主修的是化工,後來轉至研究材料領域。吳欣潔教授說:「我當時想研究綠色能源,甚至有點天馬行空地想找出完全環保的材料來發電,因為希望作對世界有意義的事情。」

因此,吳欣潔教授的實驗室稱作「高效能熱電材料與綠色能源實驗室」,那熱電材料到底是什麼呢?基本上熱電材料是以半導體材料為主,可以讓「熱」和「電」互相轉換,目前「碲化鉍 (Bi2Te3)」與「碲化鉛 (PbTe)」是最常用的兩種熱電材料。而熱電材料究竟是怎麼做到不同能量形式的轉換呢?

遇上溫度差,DoReMeSo~產生電流

首先,熱電材料是如何發電的,如同吳教授實驗室網站的第一行字「Where is a Delta-T, there is an Electricity(哪裏有溫度差,哪裏就有電)」。關鍵就在——「溫差」,我們將P型和N型半導體排列成迴路,再於兩端施加不同溫度,半導體上的電子就會往低溫處跑,電子的濃度不同而形成了電位差,便產生電流,就像瀑布會由高處往低處流,這便是所謂的塞貝克效應 (Seebeck effect),例如太空探測器便是在核反應器周圍貼上熱電元件,且熱電材料為全固態,相當安全,常用的材料系統為碲化鉛 (PbTe)。

那如果我們把發電的原理反過來,將電流通給它,也可以讓半導體電子往同一端跑,電子流動的同時也會帶走熱,進而產生溫差,達到致冷的效果,稱為皮爾特效應 (Peltier effect)。這在民生用品上較為常見,像是有些紅酒櫃便是利用熱電致冷的原理,因此不需要壓縮機,體積也可以縮小許多,常用的材料系統為碲化鉛 (PbTe)為碲化鉍 (Bi2Te3)。

茫茫材料海中能夠遇見你

那我們理解到溫差能夠產生電流後,就從此過著幸福快樂的日子了嗎?當然沒有,有句話說:「理想很豐滿,現實卻很骨感。」

而熱電材料所面臨的現實就是,大家最關心的「轉換效率」,而能夠代表熱電材料轉換效率的數值稱為「ZT 值」,ZT 值若大於 1,表示轉換效率有機會大於 10%。「如果我們想找到 ZT 值高的材料,就要它的導熱差,但導電好,目前多鎖定在半導體材料。」吳欣潔解釋。除此之外,依據塞貝克效應,會在材料的兩端施予溫差,並且期望未來能夠規模化生產,因此必須是具穩定性的材料。且希望熱電材料能夠是一種綠色能源,所以也不能含有會汙染環境的成分。總而言之,細數這些考量及條件後,發現要找到適合的熱電材料簡直比找到靈魂伴侶還難!

吳欣潔笑著說:「所以就像找伴侶一樣,先確定你的首要條件,我們做的是綠色能源,所以希望能從環境友善的材料出發。」半導體材料通常是一個母元素再參雜其他微量元素,比如常用的碲化鉛 (PbTe)之中的鉛 Pb 對環境有污染性,尋找其他可替代的發電用無鉛熱電材料,也是目前迫切之議題。

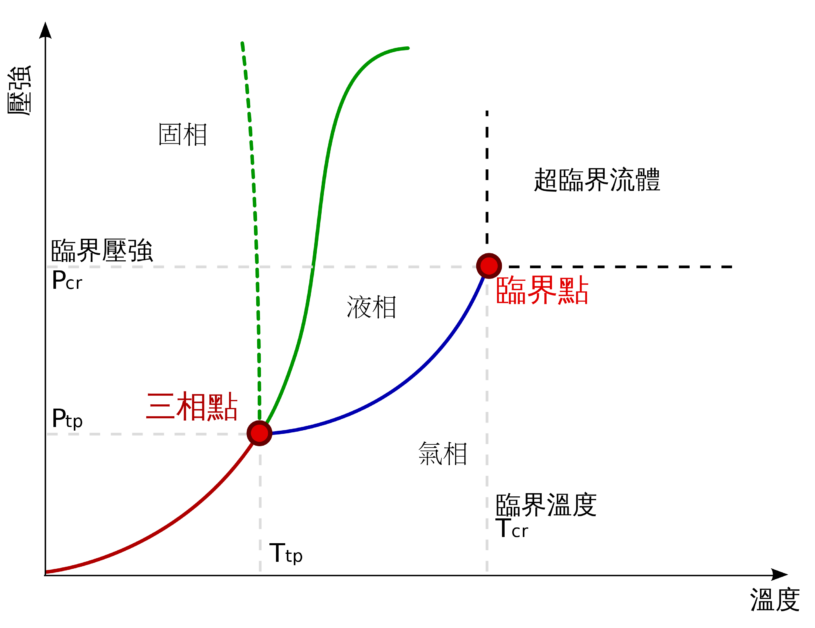

刪去不符合首要條件的元素後,接著要開始尋找適合的材料比例,吳教授的實驗室採用的方法是「相圖(phase diagram)」,它就像是材料界中的 google map,相圖可以告訴我們對這個材料而言,最好的組成配比是什麼,哪個區間的 ZT 值可能最高,哪裡的狀態最穩定。然而,要製作出一張相圖需要耗費的時間與人力成本十分可觀,但相圖資料庫的累積卻對未來材料科學的發展有很大的幫助,因此吳欣潔也希望,之後可以和人工智慧結合,加速數據的分析以及材料系統的研究。

用熱發電行不行?熱電材料的未來發展

吳欣潔也提及,熱電材料的研究需要跨領域的專業,例如化工、物理、電機、製成等,台灣在 2019 年成立了台灣熱電學會,希望能夠推廣熱電相關學術研究在台灣的普及,提升基礎研究與產業界的交流。

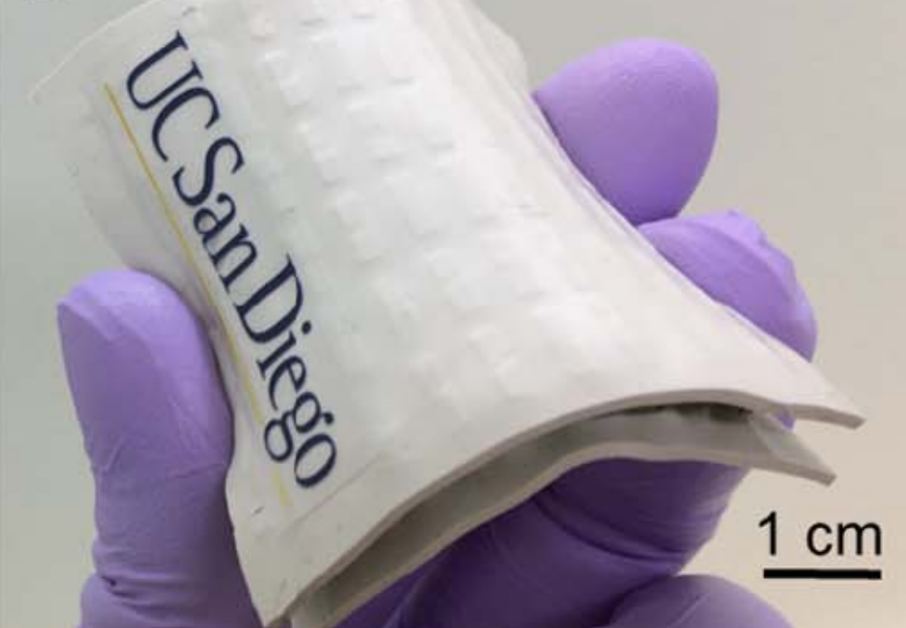

關於熱電材料未來的發展,吳教授表示,未來若能將環境中大量的廢熱回收,就能大幅度減緩溫室效應及能源耗竭的問題。在民生用途上,或許能夠在穿戴式裝置安裝熱電元件,利用人體體溫及環境的溫差來發電。

此外,吳教授說,台灣在熱電材料領域有一定的優勢,例如環境上我們有地熱溫泉,而她也認為台灣的學生相當聰明且基礎訓練佳,適合進行前端研究。在「找材料比找伴侶還難」的熱電材料領域進行研究,或許會遇到很多瓶頸,但吳教授卻說:「做研究的每天都有挫折,每天都有不盡人意的事情,但我覺得重點是從甚麼角度看待,保持樂觀、彈性的態度,就會覺得每一天都有新的發現。」