本文由 ASM 委託,泛科學企劃執行。

以人類現在的科技,我們能精準打造出每一面牆只有原子厚度的房子嗎?在半導體的世界,我們做到了!

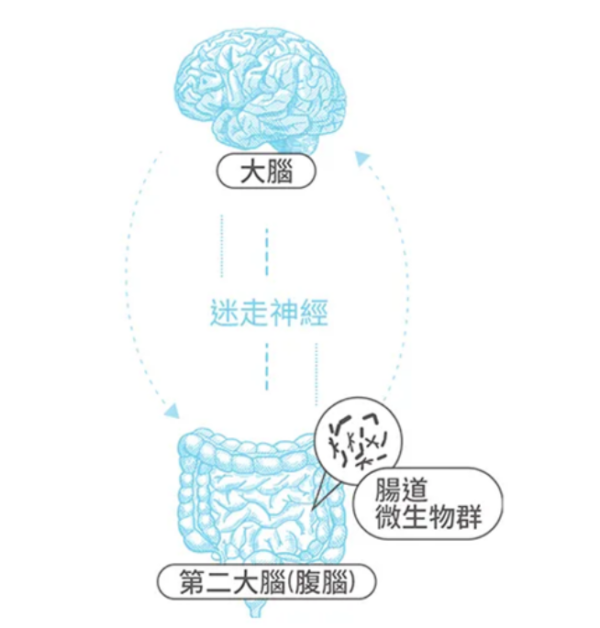

如果將半導體製程比喻為蓋房子,「薄膜製程」就像是在晶片上堆砌層層疊疊的磚塊,透過「微影製程」映照出房間布局 — 也就是電路,再經過蝕刻步驟雕出一格格的房間 — 電晶體,最終形成我們熟悉的晶片。為了打造出效能更強大的晶片,我們必須在晶片這棟「房子」大小不變的情況下,塞進更多如同「房間」的電晶體。

因此,半導體產業內的各家大廠不斷拿出壓箱寶,一下發展環繞式閘極、3D封裝等新設計。一下引入極紫外曝光機,來刻出更微小的電路。但別忘記,要做出這些複雜的設計,你都要先有好的基底,也就是要先能在晶圓上沉積出一層層只有數層原子厚度的材料。

現在,這道薄膜製程成了電晶體微縮的一大關鍵。原子是物質組成的基本單位,直徑約0.1奈米,等於一根頭髮一百萬分之一的寬度。我們該怎麼精準地做出最薄只有原子厚度,而且還要長得非常均勻的薄膜,例如說3奈米就必須是3奈米,不能多也不能少?

這唯一的方法就是原子層沉積技術(ALD,Atomic Layer Deposition)。

小小的電晶體是怎麼做出來的? 蓋房子的第一步是什麼?沒錯,就是畫設計圖。只不過,在半導體的世界裡,我們不需要大興土木,就能將複雜的電路設計圖直接印到晶圓沉積的材料上,形成錯綜複雜的電路 — 這就是晶片製造的最重要的一環「微影製程」。

首先,工程師會在晶圓上製造二氧化矽或氮化矽絕緣層,進行第一次沉積,放上我們想要的材料。接著,為了在這層材料上雕出我們想要的電路圖案,會再塗上光阻劑,並且透過「曝光」,讓光阻劑只留下我們要的圖案。一次的循環完成後,就會換個材料,重複沉積、曝光、蝕刻的流程,這就像蓋房子一樣,由下而上,蓋出每個樓層,最後建成摩天大樓。

薄膜沉積是關鍵第一步,基底的品質決定晶片的穩定性。但你知道嗎?不只是堆砌磚塊有很多種方式,薄膜沉積也有多樣化的選擇!在「薄膜製程」中,材料學家開發了許多種選擇來處理這項任務。薄膜製程大致可分為物理和化學兩類,物理的薄膜製程包括蒸鍍、濺鍍、離子鍍、物理氣相沉積、脈衝雷射沉積、分子束磊晶等方式。化學的薄膜製程包括化學氣相沉積、化學液相沉積等方式。不同材料和溫度條件會選擇不同的方法。

化學氣相沉積是現今最常見的沉積技術 二氧化矽、碳化矽、氮化矽這些半導體材料,特別適合使用化學氣相沉積法(CVD, Chemical Vapor Deposition)。CVD 的過程也不難,氫氣、氬氣這些用來攜帶原料的「載氣」,會帶著要參與反應的氣體或原料蒸氣進入反應室。當兩種以上的原料在此混和,便會在已被加熱的目標基材上產生化學反應,逐漸在晶圓表面上長出我們的目標材料。

如果我們想增強半導體晶片的工作效能呢?那麼你會需要 CVD 衍生的磊晶(Epitaxy )技術!磊晶的過程就像是在為房子打「地基」,只不過這個地基的每一個「磚塊」只有原子或分子大小。透過磊晶,我們能在矽晶圓上長出一層完美的矽晶體基底層,並確保這兩層矽的晶格大小一致且工整對齊,這樣我們建造出來的摩天大樓就有最穩固、扎實的基礎。磊晶技術的精度也是各公司技術的重點。

雖然 CVD 是我們最常見的薄膜沉積技術,但隨著摩爾定律的推進,發展 3D、複雜結構的電晶體構造,薄膜也開始需要順著結構彎曲,並且追求精度更高、更一致的品質。這時 CVD 就顯得力有未逮。

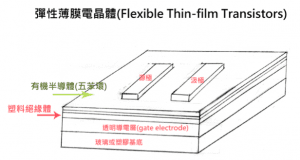

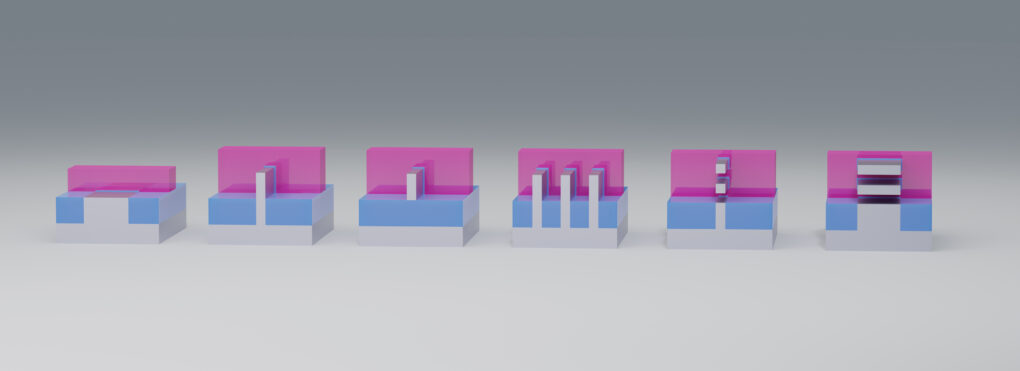

原子層沉積是什麼? 並不是說 CVD 不能用,實際上,不管是 CVD 還是其他薄膜製程技術,在半導體製程中仍占有重要地位。但重點是,隨著更小的半導體節點競爭愈發激烈,電晶體的設計也開始如下圖演變。

圖/Shutterstock 看出來差別了嗎?沒錯,就是構造越變越複雜!這根本是對薄膜沉積技術的一大考驗。

舉例來說,如果要用 CVD 技術在如此複雜的結構上沉積材料,就會出現像是清洗杯子底部時,有些地方沾不太到洗碗精的狀況。如果一口氣加大洗碗精的用量,雖然對杯子來說沒事,但對半導體來說,那些最靠近表層的地方,就會長出明顯比其他地方厚的材料。

該怎麼解決這個問題呢?

CVD 容易在複雜結構出現薄膜厚度不均的問題。圖/ASM 材料學家的思路是,要找到一種方法,讓這層薄膜長到特定厚度時就停止繼續生長,這樣就能確保各處的薄膜厚度均勻。這種方法稱為 ALD,原子層沉積,顧名思義,以原子層為單位進行沉積。其實,ALD 就是 CVD 的改良版,最大的差異在所選用的化學氣體前驅物有著顯著的「自我侷限現象」,讓我們可以精準控制每次都只鋪上一層原子的厚度,並且將一步驟的反應拆為兩步驟。

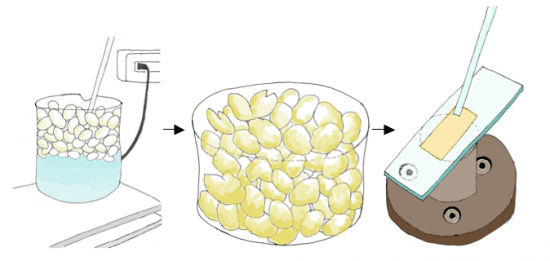

在 ALD 的第一階段 ,我們先注入含有 A 成分的前驅物與基板表面反應。在這一步,要確保前驅物只會與基板產生反應,而不會不斷疊加,這樣,形成的薄膜,就絕對只有一層原子的厚度。反應會隨著表面空間的飽和而逐漸停止,這就稱為自我侷限現象。此時,我們可以通入惰性氣體將多餘的前驅物和副產物去除。在第二階段,我們再注入含有 B 成分的化學氣體,與早已附著在基材上的 A 成分反應,合成為我們的目標材料。

透過交替特殊氣體分子注入與多餘氣體分子去除的化學循環反應,將材料一層一層均勻包覆在關鍵零組件表面,每次沉積一個原子層的薄膜,我們就能實現極為精準的表面控制。

ASM 與 ALD、半導體產業攜手前進 你知道 ALD 領域的龍頭廠商是誰嗎?這個隱形冠軍就是 ASM !ASM 是一家擁有 50 年歷史的全球領先半導體設備製造廠商,自 1968 年,Arthur del Prado 於荷蘭創立 ASM 以來,ASM 一直都致力於推進半導體製程先進技術。2007 年,ASM 的產品 Pulsar ALD 更是成為首個運用在量產高介電常數金屬閘極邏輯裝置的沉積設備。至今 ASM 不僅在 ALD 市場佔有超過 55% 的市佔率,也在 PECVD、磊晶等領域有著舉足輕重的重要性。

ASM 一直持續在快速成長,現在在北美、歐洲、及亞洲等地都設有技術研發與製造中心,營運據點廣布於全球 15 個地區。ASM 也很看重有「矽島」之稱的台灣市場,目前已在台灣深耕 18 年,於新竹、台中、林口、台南皆設有辦公室,並且在 2023 年於南科設立培訓中心,高雄辦公室也將於今年年底開幕!

當然,ALD 也不是薄膜製程的終點。

ASM 是一家擁有 50 年歷史的全球領先半導體設備製造廠商。圖/ASM ASM 作為半導體設備領導廠商,為了維持領先優勢,當然也得持續開發新技術。例如 PEALD,ALD 前面的 PE,是 Plasma Enhanced,所以這種改良技術就稱為電漿輔助式原子層沉積。做法是針對 ALD 的第一步,先以電漿方式,將氫、氧、氮等氣體電離成離子。這些氣體離子,例如氧自由基,會先將前驅物提前氧化,同時也氧化基材的表面原子,使其產生缺少電子配對、不穩定的「懸空鍵」。如此被活化的基材與前驅物,就更容易互相產生反應,解決過去 ALD 常遇到前驅物反應率不足的問題。讓反應溫度更低的同時還能加快反應速度,因此能滿足更多的製程需求。未來不論是 GAA 環繞式閘極電晶體還是其他製程,都會持續看到 ALD 技術的身影。

最後,ASM 即將出席由國際半導體產業協會主辦的 SEMICON Taiwan 策略材料高峰論壇和人才培育論壇,就在 9 月 5 號的南港展覽館。如果你想掌握半導體產業的最新趨勢,絕對不能錯過!

圖片來源/ASM