半導體產業崛起,我們常聽到「能隙」這個名詞,到底能隙是什麼?能隙越寬的材料又代表什麼意義呢?

近幾年 5G、電動車、AI 蓬勃發展,新聞常說要靠第三類的「寬能隙半導體」發展,到底寬能隙半導體在紅什麼?我們一起來了解吧!

本文轉載自宜特小學堂〈第三類寬能隙半導體到底在紅什麼?〉,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

什麼是能隙(Band Gap)?寬能隙又是「寬」在哪裡?

身為理組學生或是工程師,甚至是關心科技產業的一般人,對於「能隙」兩字一定不陌生,但你了解什麼是能隙嗎?

能隙基本上要用量子物理的理論來跟大家說明,「能帶(Band)」的劃分主要為低能帶區的「價電能帶」(Valence Band,簡稱 VB),與高能帶區「導電能帶」(Conduction Band,簡稱 CB)的兩種,在 VB 與 CB 之間即是一個所謂的能帶間隙(Band Gap,簡稱 BG),簡稱「能隙」。

金屬材料能夠導電,主要是因為電子都位於高能的(CB)區域內,電子可自由流動;而半導體材料在常溫下,主要電子是位於低能的(VB)區域內而無法流動,當受熱或是獲得足夠大於能隙(BG)的能量時,價電能帶內電子就可克服此能障躍遷至導電能帶,就形成了導電特性。

我們都知道功率等於電流與電壓加乘的正比關係,在高功率元件(Power device)的使用上如果半導體材料的能隙越寬,元件能承受的電壓、電流和溫度都會大幅提升。大眾所熟知的第一類半導體材料——矽(Si)能隙為 1.12 eV,具有成熟的技術與低成本優勢,廣泛應用於消費性電子產品;第二類半導體材料——砷化鎵(GaAs) 能隙為 1.43eV,相比第一類擁有高頻、抗輻射的特性,因此被廣泛應於在通訊領域。

為什麼需要用到第三類寬能隙半導體(Wide Band Gap,WBG)?

由於近年地球暖化與碳排放衍生的環保問題日益嚴重,世界各國都以節能減碳、綠色經濟為共同的首要發展方向,石化能源必須逐步減少並快速導入綠能節電的應用,因此不論是日常用品、交通運輸或軍事太空都逐步以高能效、低能耗為目標。

歐洲議會在 2023 年通過新法提高減碳目標,為 2030 年減碳 55% 的目標鋪路。國際能源署(IEA)也強建議各國企業在 2050 年前達到「淨零排放」,甚至有傳聞歐盟將通過燃油車禁售令,不論是考量環保或經濟,全球企業的綠色轉型勢在必行。因此在科技發展日新月異的同時,要兼顧大幅提升與改善現有的能源,已是大勢所趨。

目前半導體原料最大宗,是以第一類的矽(Si)晶圓的生產製造為主,但是以低能隙的半導體材料為基礎的產品,物理特性已到達極限,在溫度、頻率、功率皆無法突破,所以具備耐高溫高壓、高能效、低能耗的第三類寬能隙半導體(Wide Band Gap,WBG)就在此背景之下因應而生。

現在有哪些的寬能隙(WBG)材料?

那麼有哪些更佳的寬能隙材料呢?目前市場所談的第三類半導體是指碳化矽(SiC)和氮化鎵(GaN),第三類寬能隙半導體可以提升更高的操作電壓,產生更大的功率並降低能損,相較矽元件的體積也能大幅縮小。

Si 與 C 的化合物碳化矽(SiC)材料能隙可大於 3.0eV;Ga 與 N 或 O 的化合物氮化鎵(GaN)或氧化鎵(Ga2O3)能隙也分別高達 3.4eV 與 4.9eV,大家可能沒想到的是鑽石的能隙更高達 5.4eV。

| 特性 | Si 矽 | SiC(4H) 碳化矽 | GaN 氮化鎵 | Ga2O3(β) 氧化鎵 | Diamond 鑽石 |

| 能隙(eV) | 1.1 | 3.3 | 3.4 | 4.9 | 5.4 |

| 遷移率 (cm2/Vs) | 1400 | 1000 | 1200 | 300 | 2000 |

| 擊穿電場強度 (MV/cm) | 0.3 | 2.5 | 3.3 | 8 | 10 |

| 導熱率 (W/cmK) | 1.5 | 4.9 | 1.3 | 0.14 | 20 |

氮化鎵(GaN)或氧化鎵(Ga2O3),雖然分別在 LED 照明或是紫外光的濾光光源,已經應用一段時間,但受限於這類半導體材料的特性,其實生產過程充滿了挑戰。例如:要製作 SiC 的單晶晶棒,相較 Si 晶棒的生產困難且時間緩慢很多,以及 GaN 與 Si 晶圓的晶格不匹配時,容易生成差排缺陷(Dislocation Defect)等問題必須克服,導致長久以來相關的製程開發困難及花費高昂,但第三類半導體市場潛力無窮,對於各國大廠來說仍是兵家必爭之地。

寬能隙半導體運用在那些產品上?

現在知名大廠如意法半導體、英飛凌、羅姆等,對寬能隙材料的實際運用均有相當大的突破,如氮化鎵(GaN)在以 Si 或 SiC 為基板的產品已陸續發表,而我們最常接觸到的產品,就是市售的快速充電器,採用的就是 GaN on Si 材料製作的高功率產品。

除了功率提升,因為溫度與熱效應可大幅降低,元件就可以大幅縮小,充電器體積也更加玲瓏小巧,除了已商品化的快充電源領域,第三類半導體在 AI、高效能運算、電動車等等領域的應用也是未來可期。

(延伸閱讀:泛科學—快充怎麼做到又小又快? 半導體材料氮化鎵,突破工作頻率極限)

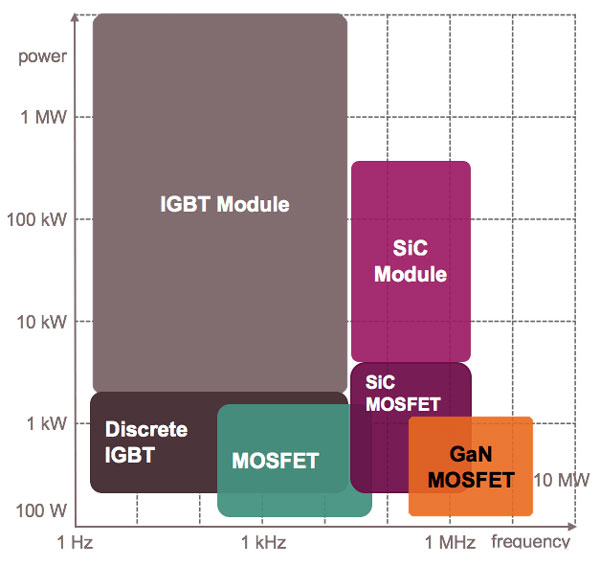

現行以矽基材料為主的高功率產品,多以絕緣閘雙極電晶體(IGBT)或金氧半場效電晶體(MOSFET)為主,下圖可以看到各種功率元件、模組與相關材料應用的範圍,傳統 IGBT 高功率模組大約能應用至一百千瓦(100Kw)以上,但速度卻無法提升至一百萬赫茲(1MHz)。而 GaN 材料雖然速度跟得上,但功率卻無法達到更高的一千瓦(1kW)以上,必須改用 SiC 的材料。

SiC 具有比 Si 更好的三倍導熱率,使得元件體積又可以更小,這些特性使它更適合應用在電動車領域。特斯拉的 model3 也從原先的 IGBT ,改成使用意法半導體生產的 SiC 功率元件,應用在其牽引逆變器(Traction inverter)、直流電交互轉換器與充電器(DC-to-DC converter & on-board charger),能夠提高電能使用效率與降低能損。

在未來更高的電力能源需求下,車載裝置除了基本要具備高功率,還需要極高速的充電能力來因應電力補充,車用充電樁、5G 通訊基地台、交通運輸工具、甚至衛星太空站等更大的電力能源需求,相關的電流傳輸轉換,電傳速度的要求以及降低能損,就必須邁向更有效率的寬能隙材料著重進行開發,超高功率的 SiC 元件模組需求亦會水漲船高。

寬能隙半導體在開發生產階段,需進行那些驗證分析?

根據宜特的觀察,晶圓代工廠與功率 IDM 廠商正持續努力研究與開發。不過,新半導體材料在開發初期,會有許多需要進行研發驗證的狀況,近年我們已協助多家寬能隙半導體(WBG)產業的開發與生產驗證。

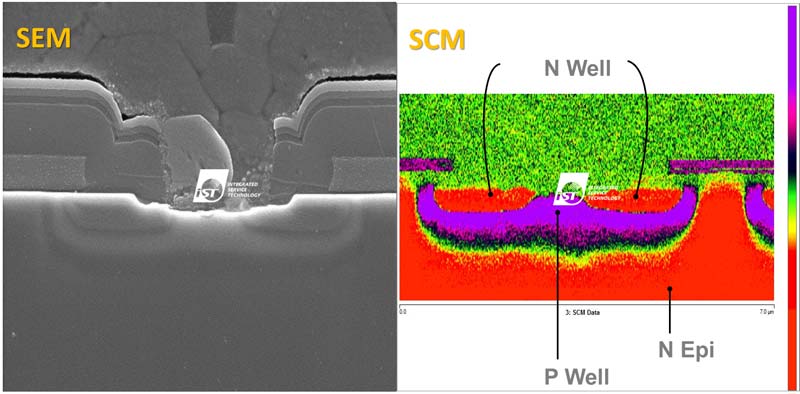

比如磊晶製程相關的結構或缺陷分析,就可以藉由雙束聚焦離子束(Dual beam FIB)製備剖面樣品並進行尺寸量測或成分分析(EDS),亦可搭配穿透式電子顯微鏡(TEM)進行奈米級的缺陷觀察;擴散區域的分析可經由樣品研磨製備剖面後,進行掃描式電子顯微鏡(SEM)觀察以及掛載在原子力顯微鏡 (AFM) 上的偵測模組-掃描式電容顯微鏡(SCM)判別摻雜區域的型態與尺寸量測。

下圖為 SiC 的元件分析擴散區摻雜的型態,我們可以先用 SEM 觀察井區(Well)的分布位置,再經由 SCM 判斷上層分別有 N 與 P 型 Well 以及磊晶層(EPI) 為 N 型。

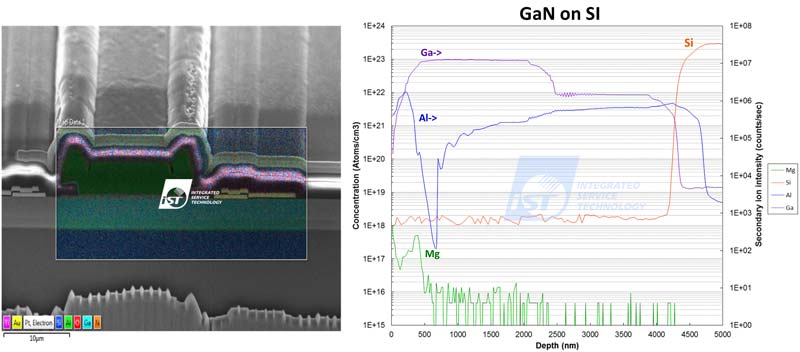

另外在摻雜元素及濃度的分析,則可透過二次離子質譜分析儀(SIMS)的技術,下圖 GaN on Si 的元件,先用雙束聚焦離子束(Dual beam FIB)進行剖面成份分析(EDS)判斷磊晶區域的主要成份之後,提供 SIMS 參考再進行摻雜元素 Mg 定量分析濃度的結果,作為電性調整的依據。

除了上述介紹 WBG 元件結構的解析之外,其它產品也都可以透過宜特實驗室專業材料分析及電性、物性故障分析來尋求解答,包括因應安全要求更高的產品可靠度測試與評估,藉由宜特可以提供更完整與全方位的驗證服務。

希望透過本文介紹,讓大家對第三類半導體有更進一步的了解,近期被稱為第四類半導體的氧化鎵(Ga2O3)也逐漸躍上檯面,它相較於第三類半導體碳化矽(SiC)與氮化鎵(GaN),基板製作更加容易,材料也能承受更高電壓的崩潰電壓與臨界電場,半導體材料的發展絕對是日新月異,也代表未來會有更多令人期待的新發現。

本文出自 www.istgroup.com。