測試 Pass 但晶片卻還是被退貨?車用工程師必讀的「避坑指南」

晶片在廠內跑了幾千小時可靠度驗證後電性 Pass,原本以為訂單穩了,結果送到 Tier 1 廠進料檢驗卻爆出「焊點裂紋」整批被退。不只研發心血白費,連剛拿到的 Design Win 都危險。到底要怎麼做,才能在驗證階段就揪出這些隱形成本,真正做到「零缺陷」?

本文轉載自宜特 小學堂〈車用工程師惡夢!為何晶片通過 ATE 測試仍遭退貨?〉 ,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

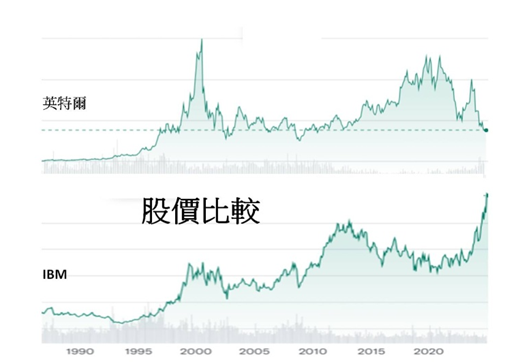

進入 2026 年,隨著「軟體定義車輛(Software-Defined Vehicle, 簡稱SDV)」 與「區域架構」(Zonal Architecture) 成為產業主流,在 SDV趨勢下,晶片需具備極高的效能餘裕以支援未來的軟體升級;而區域架構則讓大部分的晶片必須安裝在更靠近馬達等熱源與震動源位置,而在高壓、高熱、高震動的極端環境下運作。

近期 AEC 車電協會(Automotive Electronics Council)頻繁針對先進封裝修正測試標準,正是體認到 ATE(Automatic Test Equipment)電性數據已無法全面涵蓋結構疲勞的風險。包含 Tesla、NVIDIA 與高通(Qualcomm)等大廠,在將高性能運算(HPC)晶片導入車載系統時,已將「Zero Defect」的要求從晶片的「功能正常」提升至「結構絕對完整」。若您的產品潛伏結構隱患,即使僥倖通過 ATE 測試,也難逃時間的審判。

事實上,ATE Pass 僅代表「功能」合格,而 DPA(破壞性物理分析)才是驗證「壽命與結構」的關鍵。 若不想讓即將到手的量產門票毀於一旦,在研發階段就導入 DPA 進行深度的物理診斷,是邁向車規級零缺陷的必經之路。因此,本篇《宜特小學堂》將透過 DPA(Destructive Physical Analysis,破壞性物理分析)剖析三大案例,助您的車用產品安全上路。

一、 什麼是 DPA?為什麼它是車規的「照妖鏡」?

簡單來說,DPA 就像是「身體健康檢查」。有別於一般 FA(故障分析) 是在壞掉後才找原因,DPA 是在產品判定「電性功能 Pass」的狀態下,隨機抽樣進行一系列的破壞性拆解與檢測。

它的目的只有一個:檢查那些「躲過 ATE 測試」的潛在性內傷。

例如:打線接合面其實已出現裂痕,但剩下的接觸面在 ATE 電性測試下導通依然良好,顯示Pass。這種晶片一旦上車,經歷幾次熱脹冷縮就會徹底斷裂。這種「未爆彈」,只有透過 DPA 把它切開來看,才能無所遁形。

二、別再說客戶沒要求!AEC 早就寫得清清楚楚

很多IC設計工程師會問:「AEC-Q100 我都跑完了,客戶也沒特別說要做 DPA,我有必要多花這筆錢嗎?」

根據 AEC 規範,DPA 絕非選配,而是確保結構品質的必要手段。除了針對分離式元件的 AEC-Q101、光電半導體的 AEC-Q102 及板階可靠度的 AEC-Q007 皆將 DPA 列為必測項目外;針對銅線(Cu Wire)製程的 AEC-Q006,更制定了最嚴格且具體的破壞性分析標準,成為所有採用銅線封裝的車用晶片必須跨越的硬性門檻。

如果你為了降低成本,而將封裝從「金線」轉為「銅線(Cu Wire)」,那麼你已經自動落入 AEC-Q006 的規範範疇。由於銅線較硬,容易在製程中造成底層鋁墊(Al Pad)破裂(Cratering),因此 AEC-Q006 明確要求必須進行 DPA 相關項目的驗證。

如果你不想被 Tier 1 稽核時抓包,以下這些是 AEC-Q006 裡提到必須關注的 DPA 重點項目:

1. Wire Bond Shear ( 焊球推力測試 ) : 透過橫向推力確認銅球與鋁墊的結合品質。檢視金屬間化合物(IMC)的生成狀況,了解打線底層介面是否有剝離或裂痕。對於 Cpk(Process Capability Index)數值分佈有嚴格要求,以證明製程能力穩定。

2. Wire Bond Pull ( 焊線拉力測試 ) : 透過垂直拉力著重測試打線頸部和第二焊點是否牢固。透過分析拉線後的失效模式(Wire pull failure modes)來了解斷裂發生的位置,與 Wire Bond Shear 一樣會確認 Cpk 數值是否於規範內。

3. Crater Test (彈坑測試): 這是銅線製程的關鍵檢查。移除焊墊金屬層,檢查下方是否有因打線應力造成肉眼看不見的「隱形裂紋(Cratering)」。

4. Cross-Section (切片分析): 使用 SEM(電子顯微鏡) 檢查整個樣品的完整性,包含晶片、模封膠(Molding compound)、黏晶膠(Die attach)、導線架(Lead frame)之間的介面狀況,以及打線第一和第二焊點下方有無微裂紋與脫層異常。

5. 內部目檢(Internal Visual): 檢查封裝體內晶片表面,是否有保護層裂紋或晶片缺角等損傷。

三、宜特案例分享:解決工程師最頭痛的隱性失效

以下是宜特協助 IC Design House 在量產前,透過 DPA 攔截的三大災難現場:

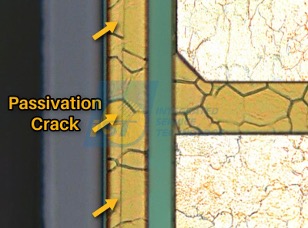

(一)案例一:護層裂紋攔截術—破解 ATE 的偵測延遲假象

某車用 IC 客戶在進行可靠度測試後,ATE 顯示全數通過。但宜特工程團隊透過 DPA 的 Phase 1 破壞性分析發現,部分樣品的 Passivation(護層)已出現微小裂紋。進一步透過橫截面觀察,確認裂紋已延伸至金屬層邊緣。

這說明了僅有電性測試卻無 DPA 攔截的狀態下,這批貨一旦裝上車,數個月後可能將引發大規模客訴甚至災難性的性命傷害疑慮。

圖一:DPA 顯示護層裂紋,暴露ATE測試中看不見的可靠度風險。圖/宜特科技

(二)案例二:銅線打線(Cu Wire)界面診斷—直擊 AEC-Q006 最在意的焊點疲勞

為了兼顧成本與效能,許多車用晶片將製程轉向銅線(Cu Wire)封裝,但這也帶來了更嚴苛的可靠度挑戰,尤其是 AEC-Q006 規範中最在意的高溫應力與金屬疲勞。在銅線封裝製程中,焊點與鋁墊間的 IMC覆蓋率是訊號傳遞可靠度的指標。

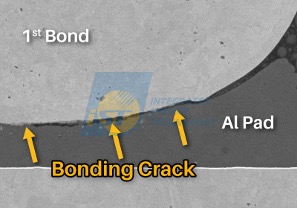

某客戶希望優化打線參數,雖然初步電性測試無異,但宜特透過 DPA 的分析與測試手法,發現特定參數下的 IMC 生長不均,且推力值雖在規格內但故障模式出現了「Bonding crack 」徵兆。這正是典型的「當下 Pass、長期 Fail」假象。

圖二:DPA 顯示焊點缺陷,暴露 ATE 測試中看不見的可靠度風險。圖/宜特科技

(三)案例三:介面分層深度定位,解決熱膨脹係數不匹配的災難

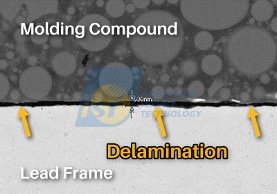

在車規可靠度測試後,宜特運用 DPA 手法,整合非破壞與破壞性分析技術,針對封裝結構進行全面性的「身體檢查」。此分析結果不僅精準定位出導線架與模封膠間的介面分層位置,更進一步溯源發現,分層主因係導線架與模封膠這兩類異質介面間的熱膨脹係數(CTE)不匹配。

這項關鍵發現不僅釐清了 Failure 原因,更提供客戶具體的改善方向,協助客戶重新篩選膠材,從根本提升了整體結構的熱機穩定性。

圖三:透過 DPA 深度切片與掃描技術來檢查封裝結構的完整性。圖/宜特科技

以電性結果通過 AEC 認證只是入場券,然而邁向「零缺陷」的核心課題,在於如何補齊電性測試看不見的盲點。對於IC設計公司而言,DPA 不應該被視為一項「多餘的成本」,而是一份「確保出貨安全的保險」。

當你的競爭對手只拿得出 ATE 報告,而你能同時附上第三方公正實驗室的 DPA 完整分析報告,這代表的不僅是品質,更是你對車規理解的專業度。別讓一顆1美元的晶片,毀了你千萬美元的訂單。在送樣給 Tier 1 之前,先透過 DPA 做最後一次的健康檢查吧!

本文出自 www.istgroup.com 。