從奈米微塵到化學氣體, HEPA 與活性碳如何聯手打造純淨空氣?

本文由 Amway 委託,泛科學企劃執行。

在半導體產業的無塵室中,「乾淨」的定義極其殘酷:一粒肉眼看不見的灰塵,就足以讓造價數百萬美元的晶圓直接報廢 / 圖片來源:envato

在半導體產業的無塵室中,「乾淨」的定義極其殘酷:一粒肉眼看不見的灰塵,就足以讓造價數百萬美元的晶圓直接報廢 / 圖片來源:envato

到底怎樣才算是「乾淨」?這不是什麼靈魂拷問,而是一個價值上億的商業命題。

在半導體產業的無塵室中,「乾淨」的定義極其殘酷:一粒肉眼看不見的灰塵,就足以讓造價數百萬美元的晶圓直接報廢。空氣品質的好壞,甚至能成為台積電(TSMC)決定是否在當地設廠的關鍵性指標。回到你的家中,雖然不需要生產精密晶片,但我們呼吸系統中的肺泡同樣精密,卻長期暴露在充滿 PM2.5、病毒以及各種揮發性氣體的環境中。為了守護健康,你可能還要付費購買「乾淨的空氣」來用。

因此,空氣議題早已超越單純的環保範疇,成為同時影響國家經濟與個人健康的重要問題。

很多人可能沒想到,無論是家用的空氣清淨機,還是造價動輒百億的頂尖晶圓廠,它們對抗污染的核心武器並非什麼複雜的雷射防護罩,而是同一件看起來平凡無奇的東西:一片外觀像紙一樣的 HEPA 濾網。但你真的相信,就憑這層厚度不到幾公分的板子,能擋住那些足以毀滅精密晶片、滲透人體細胞的「奈米級刺客」嗎?

這片大家都聽過的 HEPA 濾網,裡面到底是什麼?

首先,我們必須打破一個直覺上的誤解:HEPA 濾網(High Efficiency Particulate Air filter)在本質上其實並不是一張「網」。

細懸浮微粒 PM2.5,是指粒徑在 2.5 微米以下的污染物,它們能穿過呼吸道直達肺泡,並穿過血管引發全身性發炎。但這只是基本,在工廠與汽車尾氣中,還存在粒徑僅有 1 微米的 PM1,甚至是小於 0.1 微米的「超細懸浮微粒」(UFP,即 PM0.1)。 UFP 不僅能輕易進入血液,甚至能繞過血腦屏障(BBB),進入大腦與胎盤,其破壞力十分可怕。

如果 HEPA 濾網像水槽濾網或麵粉篩一樣,單靠孔目大小來「過濾」粒子,那麼為了攔截奈米微粒,濾網的孔目只能無限縮小到幾乎不透氣的程度。更別說在台積電或 Intel 的製程工程師眼裡,一般人認為的「乾淨」,在工程師眼裡簡直像沙塵暴一樣。對於線寬僅有 2 奈米或 3 奈米(相當於頭髮直徑萬分之一)的晶片而言,空氣中一顆微小的塵埃,就是一顆足以毀滅世界的隕石。

因此,傳統的過濾思維並非治本之道,我們需要的是原理截然不同的過濾方案。這套技術的雛形,最早可追溯至二戰時期的「曼哈頓計畫」。

HEPA 的前身,誕生於曼哈頓計畫!

1940 年代,製造濃縮鈾是發展原子彈的關鍵。然而,若將排氣直接排向大氣,會導致致命的放射性微粒擴散。負責解決這問題的是 1932 年諾貝爾化學獎得主歐文·朗繆爾(Irving Langmuir),他是薄膜和表面吸附現象的專家。他開發了「絕對過濾器」(Absolute Filter),其內部並非有孔的篩網,而是石綿纖維。

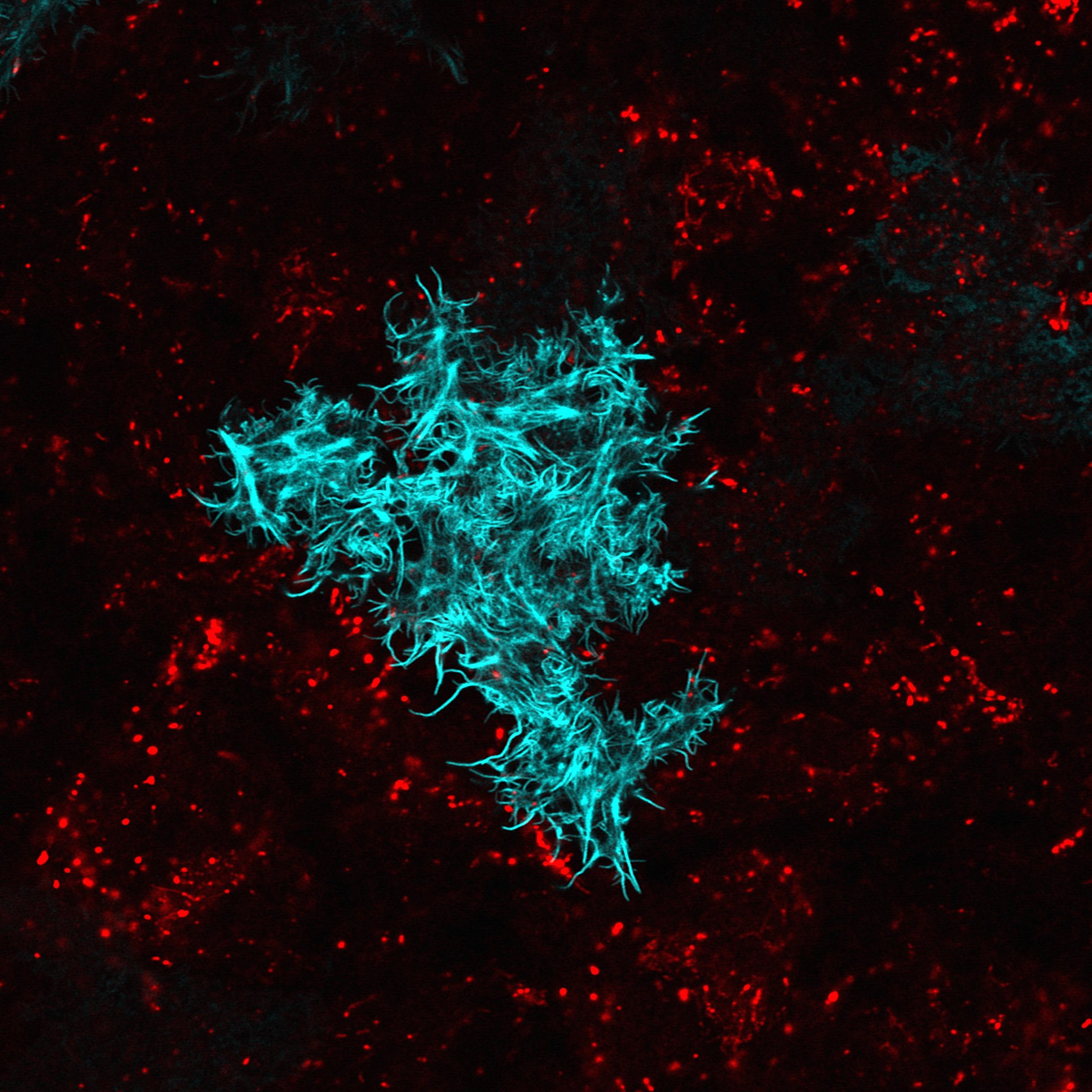

有趣的來了,如果把過濾器放到顯微鏡下,你會發現纖維之間的空隙,其實比某些被攔截的粒子還要大。那為什麼粒子穿不過去呢?這是因為在奈米尺度下,物理規則與宏觀世界完全不同。極微小的粒子在空氣中飛行時,並非走直線,而是會受到空氣分子撞擊,而產生「布朗運動」(Brownian Motion),像個醉漢一樣東倒西歪。

當粒子通過由緻密纖維構成的混亂迷宮時,布朗運動會迫使它們不斷轉彎、移動,最終撞擊到帶有靜電的纖維上。這時,靜電的吸附力會讓纖維就像蜘蛛網般死死黏住微粒。那些狂亂移動的奈米刺客,就這樣被永久禁錮迷宮中。

現在最常見的 HEPA 材料,是硼矽酸鹽玻璃纖維。

現代 HEPA 濾網最常見的核心材料為硼矽酸鹽玻璃纖維。這些玻璃纖維的直徑通常介於 0.5 至 2 微米之間,它們在濾網內隨機交織,像是一座茂密「黑森林」。微粒進入這片森林後,並非僅僅面對一層薄紙,而是得穿越一個具有厚度且排列混亂的纖維層,微粒極有可能在布朗運動的影響下撞擊並黏附在某根玻璃絲上。

除此之外,HEPA 濾網在外觀上還有一個極具辨識度的特徵,那就是像手風琴般的摺紙結構。濾材會被反覆摺疊、摺成手風琴的形狀,中間則用鋁箔或特殊的防潮紙進行結構支撐,目的是增加表面積。這不僅為了捕獲更多微粒,而是要「降低過濾風速」。這聽起來可能有點反直覺:過濾不是越快越好嗎?

其實,這與物理學中的流速控制有關。想像一條水管,如果你捏住出口,水流會變得湍急;若將出口放開並擴大,雖然總出水量不變,但出水處的流速會變得緩慢。對於 HEPA 濾網而言,當表面積越大,單位面積所需承載的空氣量就越少,空氣穿透濾網的速度也就越低。

低流速代表微粒停留在濾網內的時間也更久,增加被捕捉的機會。此外,越大的表面積也為 HEPA 濾網帶來了高「容塵量」,延長了使用壽命,這正是它能夠稱霸空氣清淨領域多年的主因。

然而,即便都叫做 HEPA 高效率空氣微粒子過濾網 (High Efficiency Particulate Air filter),但每個 HEPA 的成分與結構還是會不一樣。例如 安麗逸新空氣清淨機 SKY ,其標榜「可過濾粒徑最小至 0.0024 微米」的污染物,去除率高達 99.99%。

0.0024 微米是什麼概念?塵蟎、花粉、皮屑或黴菌孢子,大小約在 2 至 200 微米;細懸浮微粒 PM2.5 大小約 2.5 微米,細菌也大概這麼大。最小的其實是粒徑小於 0.1 微米的「超細懸浮微粒」,大多數的病毒(如流感、新冠病毒)都落在此區間。對安麗逸新 的HEPA濾網來說,基本上通通都是可被攔截的榜上名單。

在過敏防護上,它更獲得英國過敏協會(Allergy UK)認證,能有效處理 19 大類、102 種過敏原,濾除空氣中超過 300 種氣態與固態污染物。

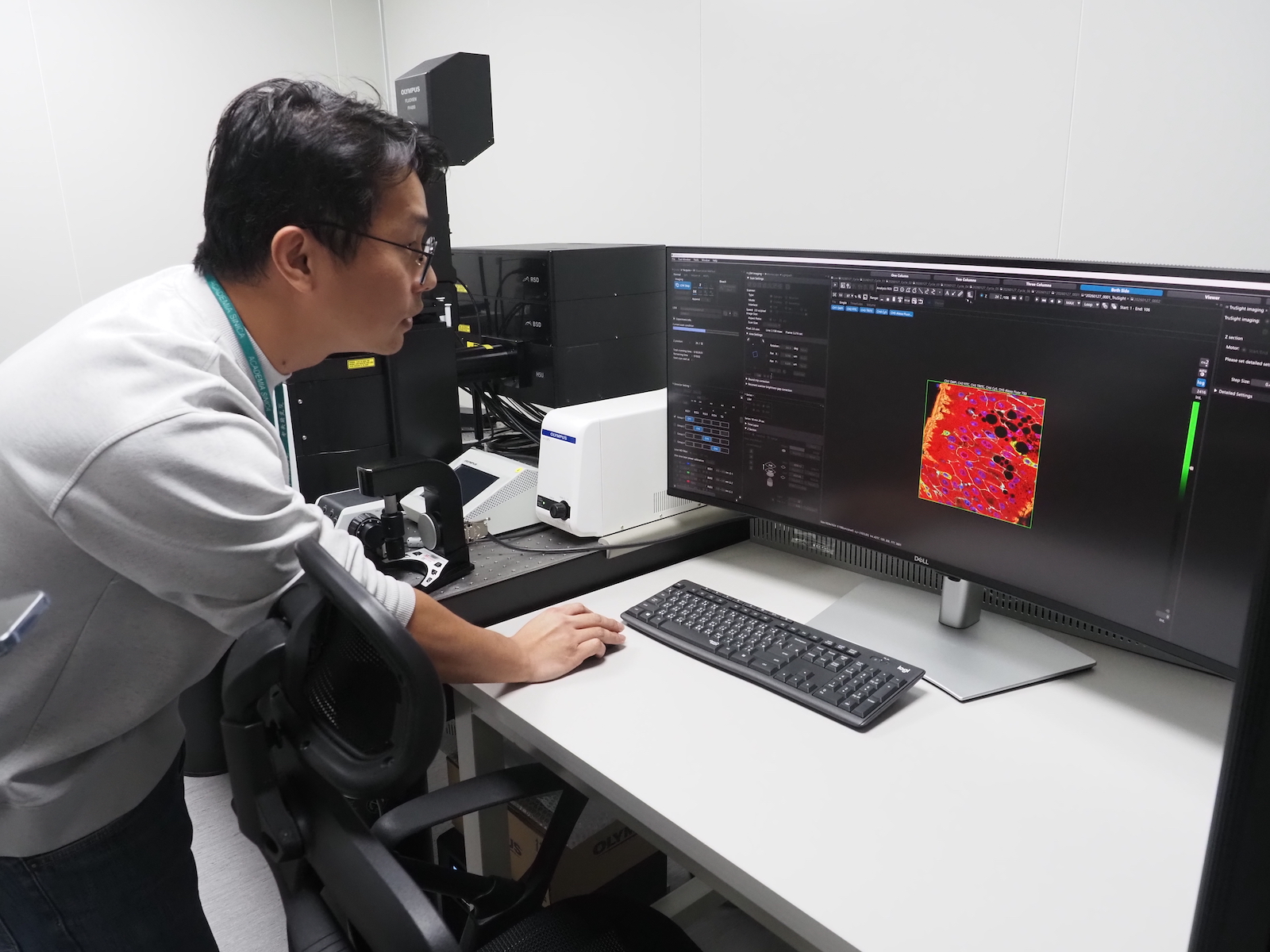

同樣的過濾邏輯一旦進入半導體無塵室,就必須換一條更為嚴苛的技術路線。因為硼矽酸鹽玻璃纖維對晶圓來說有個致命傷,就是「硼 (Boron)」 / 圖片授權:Shutterstock

同樣的過濾邏輯一旦進入半導體無塵室,就必須換一條更為嚴苛的技術路線。因為硼矽酸鹽玻璃纖維對晶圓來說有個致命傷,就是「硼 (Boron)」 / 圖片授權:Shutterstock

然而,同樣的過濾邏輯一旦進入半導體無塵室,就必須換一條更為嚴苛的技術路線。因為硼矽酸鹽玻璃纖維對晶圓來說有個致命傷,就是「硼 (Boron)」。

在半導體製程中,硼是常見的 P 型摻雜物,用來精準改變矽晶圓的電性。如果濾網有任何微小的破損、老化或化學侵蝕,進而釋放出極微量的硼離子,就可能直接污染晶圓,改變其導電特性,導致晶片報廢。

此外,無塵室要求的是比 HEPA 更極致的 ULPA(超低穿透率空氣濾網) 等級的潔淨度。ULPA 的標準通常要求對 0.12 微米 的粒子達到 99.999% 甚至 99.9999% 的超高攔截率。在奈米級的競爭中,任何多穿透的一顆微塵,都代表著一筆不小的經濟損失。

為了解決「硼」的問題並追求極限的過濾效率,材料學家搬出了塑膠界的王者,PTFE 也鐵氟龍。鐵氟龍不僅耐酸鹼、耐腐蝕,還能透過拉伸製成直徑僅 0.05 至 0.1 微米 的極細纖維,其細度遠勝玻璃纖維。雖然 PTFE 耐化學腐蝕,但它既昂貴且物理上也很脆弱,安裝時若不小心稍微觸碰,數萬元的濾網就可能報銷。因此,你只會在晶圓廠而非一般家庭環境看到它。

即便如此,在空氣濾淨系統中,還有一樣是無塵室和你家空氣清淨器上面都有的另一張濾網,就是活性碳濾網。

活性碳如何從物理攔截跨越到分子吸附?

好不容易將微塵擋在門外時,危機卻還沒有解除。因為空氣中還隱藏著另一類更難纏的大魔王:AMC(氣態分子污染物)。

HEPA 或 ULPA 這類物理濾網雖然能攔截固體微粒,但面對氣態分子時,就像是用網球拍想撈起水一樣徒勞。這些氣態分子如同「幽靈」一般,能輕易穿過物理濾網的縫隙,其中包括氮氧化物、二氧化硫,以及來自人體的氨氣與各種揮發性有機物(VOCs)。

為了對付這些幽靈,我們必須在物理防線之外,加裝一道「化學濾網」。

這道防線的核心就是我們熟知的活性碳。但這與烤肉用的木炭不同,這裡使用的是經過特殊改造的「浸漬處理(Impregnation)」活性碳。材料科學家會根據敵人的不同性質,在活性碳上添加不同的化學藥劑:

- 酸鹼中和:對付氮氧化物、二氧化硫等酸性氣體,會在活性碳上添加碳酸鉀、氫氧化鉀等鹼性藥劑,透過酸鹼中和反應將有害氣體轉化為固體鹽類。反之,如果添加了磷酸、檸檬酸等酸性藥劑,就能中和空氣中的氨氣等鹼類。

- 物理吸附與凡德瓦力:對於最麻煩的有機揮發物(VOCs,如甲醛、甲苯),因為它們不具酸鹼性,科學家會精密調控活性碳的孔徑大小,利用龐大的「比表面積」與分子間的吸引力(凡德瓦力),像海綿吸水般將特定的有機分子牢牢鎖在孔隙中。

活性碳如何從物理攔截跨越到分子吸附? / 圖片來源:Amway

活性碳如何從物理攔截跨越到分子吸附? / 圖片來源:Amway

空氣濾淨的終極邏輯:物理與化學防線的雙重合圍

在晶圓廠這種對空氣品質斤斤計較的極端環境,活性碳的運用並非「亂槍打鳥」,而是一場極其精密的對戰策略。

工程師會根據不同製程區域的空氣分析報告,像玩 RPG 遊戲時根據怪物屬性更換裝備一樣——「打火屬性怪要穿防火裝,打冰屬性則換上防寒裝」。在最關鍵的黃光微影區(Photolithography),晶圓最怕的是人體呼出的氨氣,此時便會配置經過酸性藥劑處理的活性碳進行精準中和;而在蝕刻區(Etching),若偵測到酸性廢氣,則會改用鹼性配方的濾網。這種「對症下藥」的客製化邏輯,是確保晶片良率的唯一準則。

而在你的家中,雖然我們無法像晶圓廠那樣天天進行空氣成分分析,但你的肺部同樣需要這種等級的保護。安麗逸新空氣清淨機 SKY 的設計邏輯,正是將這種工業級的精密防護帶入家庭。它不僅擁有前述的高規 HEPA 濾網,更搭載了獲得美國專利的活性碳氣味濾網。

關於活性碳,科學界有個關鍵指標:「比表面積(Specific Surface Area)」。活性碳的孔隙越多、表面積越大,其吸附能力就越強。逸新氣味濾網選用高品質椰殼製成的活性碳,並經過高溫與蒸氣的特殊活化處理,打造出多孔且極致高密度的結構。

這片濾網內的活性碳配重達 1,020 克,但其展開後的總吸附表面積竟然高達 1,260,000 平方公尺——這是一個令人難以想像的數字,相當於 10.5 個台北大巨蛋 的面積。這種超高的比表面積,是市面上常見濾網的百倍之多。更重要的是,它還添加了雙重觸媒技術,能特別針對甲醛、戴奧辛、臭氧以及各種細微的異味分子進行捕捉。這道專利塗層防線,能將你從裝潢家具散發的有機揮發氣體,或是路邊繁忙車流的廢氣中拯救出來,成為全家人的專屬空氣守護者。

總結來說,無論是造價百億的半導體無塵室,還是守護家人的空氣清淨機,其背後的科學邏輯如出一轍:「物理濾網攔截微粒,化學濾網捕捉氣體」。只有當這兩道防線同時運作,空氣才稱得上是真正的「乾淨」。

進一步了解商品:https://shop.amway.com.tw/products/2071?navigationType=brand&

http://ojps.aip.org/journals/doc/APPLAB-ft/vol_82/iss_15/2491_1-F1.jpg ” border=”0″>