雷射的原理與光學繞射極限

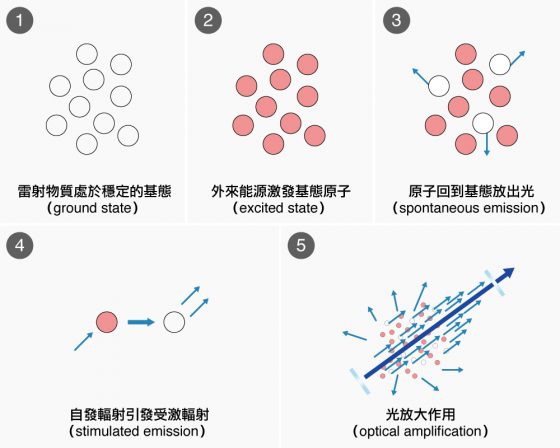

1916 年,愛因斯坦首次探討描述了原子有「自發輻射」與「受激輻射」的可能性。他認為被激發的高能態原子,會有兩種回到低能量狀態的過程。一種是自行釋放出光子而回到低能態的自發輻射;另一種則是如果照射「特定波長」的光子,可以刺激原子提前釋放出,與原照射光波長相同光子的受激輻射。

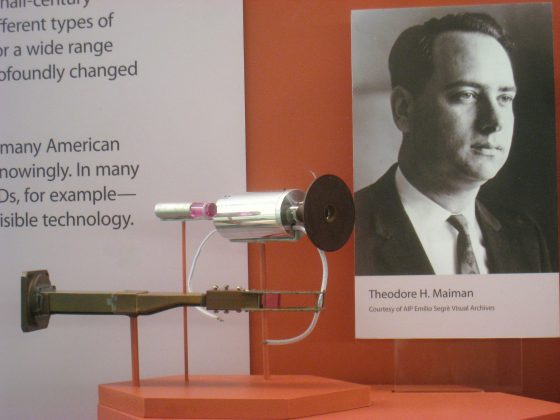

1958 年, Charles H. Townes 在分子光譜學的研究中,構想出可利用「受激輻射」的原理來得到指定波長的光;他的同事 Arthur L. Schawlow 提出在激發出光的物質兩端,裝上兩面反射鏡,讓激發光不斷在物質內部來回來反射,由於「受激輻射」的發射速率超過吸收速率,透過此構想,便可實現光放大效應,讓指定波長的光不斷地增強。

1962 年, Robert N. Hall 等人,提出利用外加偏壓,讓半導體中價電帶的電洞與導電帶的電子產生能階差,當高能階的電子躍遷回價電帶與電洞結合時,能量便會以「光子」的形式釋出,釋出的光子會在半導體 PN 接面之間,因為半導體的光滑晶格面,而不斷反射累積光能量,形成「共振腔」的結構,而設計出「半導體雷射」。

今日我們所稱的「雷射 (LASER) 」,就是「受激輻射所產生的光放大 (Light Amplification by Stimulated Emission of Radiation)」的縮寫。

「雷射」其原理是先利用輻射,刺激特定的物質,讓物質內原子受到激發,使其最外層的電子躍遷至較高的能階。

當電子處於高能階時,再給予特定頻率的輻射(光)照射,而使電子躍遷回較低的能階,並釋放出與照射光相同頻率的光子。如果,我們將產生光子的原子,利用兩個設置於雷射物質兩端的反射鏡,讓光子在雷射物質內來回反射,而繼續激發更多的電子躍遷,就能夠不斷累積同頻率的光子。

在這兩面反射鏡中,其中一面能完全反射光子,另一面則允許小部分光子穿過,所穿過的光子束即為雷射,具有發散低、功率高的特性。小至單一晶片的二極體雷射,大至用作促成核融合的釹玻璃雷射,都是雷射的應用尺度。

然而,對於微電子元件的設計上,雷射元件的「微型化」一直有其阻礙。這是由於能促成雷射功率不斷放大增強的關鍵,是由兩個具有反射效果的反射鏡或反射材質,所組成的共振腔。

在過往的研究中,共振腔受到「繞射極限」的限制,最短需要半個波長的大小,以波長 650 奈米的紅光雷射來看,共振腔的長度至少需要 325 奈米。相比起今日各類電晶體元件已能做到十幾奈米的尺寸,光子元件的微型之路,因為光學「繞射極限」這個基本物理限制,而遭受到了阻礙。

電漿子共振腔 縮小雷射元件的體積

以「電漿子共振腔」取代「傳統光學共振腔」,就能將雷射元件體積減少到遠小於可見光波長的奈米尺度!

2012 年,還在就讀清華大學物理學系博士班二年級的呂宥蓉,在果尚志教授的研究團隊中,將「單根氮化銦鎵奈米柱」與「電漿子共振腔 (plasmonic cavity)」 結合,取代傳統光學共振腔,將雷射元件體積減少到遠小於可見光波長的奈米尺度,開發出史上最小的電漿光子奈米雷射。並證明利用電漿子共振腔,可使半導體雷射元件不受限於光學繞射極限,而能大幅縮小雷射元件尺寸。

這是由於研究團隊所開發的電漿光子奈米雷射中,對於雷射功率的增益,並非利用傳統由兩面具有反射效果的材質所組成的光學共振腔,而是改以「電漿子共振腔」取代。

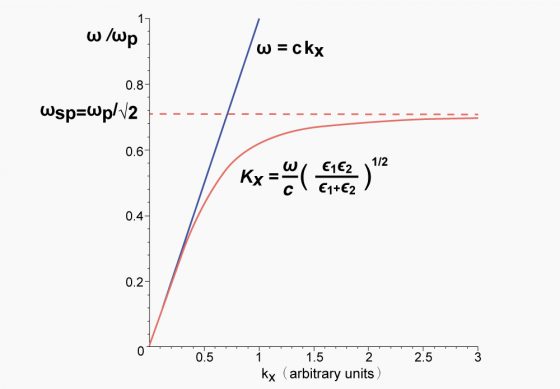

電漿子共振腔是由「金屬-氧化物-半導體 (Metal-Oxide-Semiconductor, MOS) 」所組成的奈米結構。這是利用金屬在與介電質(氧化物)的交界面,會有形成表面電漿極化子 (surface plasmon polariton, SPP)的特性。

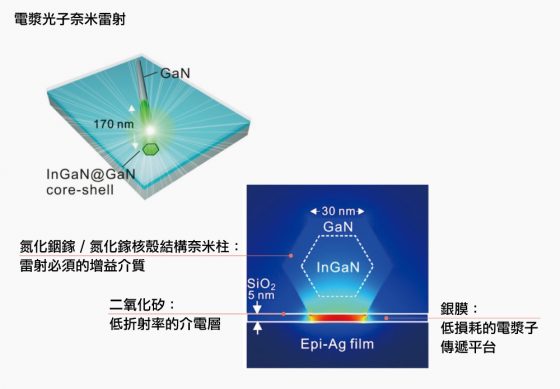

因此,研究團隊在矽基板上,與德州大學奧斯丁分校物理系施志剛教授合作,利用磊晶技術長出一片原子層平坦的銀膜 (Epi-Ag film)作為低損耗的電漿子傳遞平台,在其上鍍一層五奈米厚的二氧化矽 (SiO2) 作為低折射率的介電層,最後放上利用分子束磊晶技術製作的氮化銦鎵/氮化鎵核殼結構奈米柱 (InGan@GaN core-shell nanorods)作為雷射必須的增益介質。

氮化銦鎵/氮化鎵核殼結構奈米柱是一個各邊邊長 30 奈米的六角形晶柱。當外加能量激發奈米柱時,氮化銦鎵會釋放出「光子」。這些光子,與銀膜和二氧化矽介電層之間的表面電漿極化子共振頻率均在「可見光」波段,光子與表面電漿極化子之間並有一對一的對應狀態,能讓光子與表面電漿極化子產生耦合形成混成態。

這讓「光子」因為與「電漿子」耦合,而被侷限在「二氧化矽介電層」之中不斷累積能量,如同傳統雷射的光學共振腔,但卻不受繞射極限的限制。

光運算、光通訊效能 有機會大幅提升

不受繞射極限的電漿共振腔,讓雷射元件的尺寸大幅縮小至數十奈米的級別,不僅尺寸上與今日積體電路製程常用的「互補式金屬氧化物半導體 (Complementary Metal-Oxide-Semiconductor, CMOS)」可互相匹配,且同為 MOS 的結構。

「電漿子奈米雷射元件」的發明,意味我們將有機會在電子元件的架構上,利用雷射元件發展高速、寬頻、低功耗的光運算器與光通訊系統。

突破光學的繞射極限,為光運算與光通訊時代奠定了關鍵的基礎。但呂宥蓉認為這個領域在未來仍有許多有待發展的方向,例如研發「電激發光」的奈米雷射來取代現有的「光激發」奈米雷射;或是將雷射的應用環境,從目前主流的低溫研究拓展至室溫中,可為未來在積體電路上整合光電元件有所助益。

另外,該研究也有助於在生物醫學應用上發展超高解析生物影像;在材料上減少貴金屬的使用,改研發低損耗的陶瓷電漿子材料——氮化鈦、氧化銦錫、氮化鋯,此為在美國加州理工做博士後研究兩年期間獲得的靈感。同時因應目前單光子材料開始受到重視,呂宥蓉也計畫研究可以電壓控制之單光子的行為。

最終能更理解材質與光的特性,化為操作光的技術,應用至生物感測器、量子電腦、可撓式顯示器等尖端科技。

「我喜歡思考有什麼可以做,並真的做出來!」

傑出的研究成果與高瞻遠矚的發展眼光,往往來自長年努力的累積與幸運的眷顧。呂宥蓉在碩二、博一期間連續在以第一或主要作者,登上 APL 封面論文,博二時更以不受限於光學繞射極限的「電漿光子奈米雷射」研究成果,刊登於 Science 期刊。

面對如此進展迅速的研究成果,呂宥蓉謙虛地表示,這其實沒有什麼特別的秘訣,也不能算是進展比別人快,只是把一天 24 小時當成 36 小時用,犧牲了睡眠與娛樂機會,才能有這些成果。

奮不顧身的研究投入,植基於對科學的熱愛、對自我專長的理解、與環境的支持。呂宥蓉從大學期間,就發現自己熱愛實驗與儀器組裝、操作,喜歡想像並嘗試各種材料與理論的組合。更重要的,是求學期間指導教授果尚志老師,認為研究生應有獨立研究能力與追求科學價值的治學理念。

知止而後有定,定而後能靜,靜而後能安,安而後能慮,慮而後能得。

呂宥蓉特別引用了《大學》裡的前人智慧,與同在研究之路上的學弟妹們勉勵,也為今日的成就下了安心踏實的註腳。

參考資料

本著作由研之有物製作,以創用CC 姓名標示–非商業性–禁止改作 4.0 國際 授權條款釋出。

本文轉載自中央研究院研之有物,泛科學為宣傳推廣執行單位